FPGAベンダのLattice Semiconductorは5月24日、都内で会見を開き、2010年11月に同社President and CEOに就任したDarin G. Billerbeck氏が就任以来、初めて日本でのプレス向け説明を行った。

|

|

|

Lattice SemiconductorのPresident and CEOであるDarin G. Billerbeck氏 |

同社が注力する製品分野はFPGAの中でもLUTが比較的少ないミッドレンジおよびローデンシティ分野、そしてアナログ関連のミクスドシグナル・ボード管理分野の3つ。3分野の中では比較的LUT数の多いミッドレンジは無線/有線通信基地局やカメラ、ディスプレイなどで適用されており、一方のLUTが少なめのローデンシティは、低コスト、低消費電力の特長を生かして携帯機器やTV、LCD、制御/グルーロジックなどでの適用、そしてミクスドシグナル・ボード管理は通信インフラや産業機器、ネットワーク機器などのパワーマネジメントなどに活用されている。

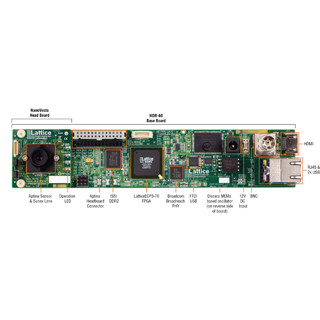

それぞれの領域に適合する製品としてはミッドレンジFPGAでは「ECP3」があり、同ファミリの最大の武器を同氏は「低消費電力と低コスト、そして3GbpsのSerDesやDDR3メモリインタフェースなどの充実した各種機能」だと説明する。また、ローデンシティ向けではPLD「Mach XO2」であり、「低コストと低消費電力が武器。パッケージも小型で携帯機器や小型フォームファクタなどのサイズを重要視する分野でも活用できる」と説明する。そしてミクスドシグナル分野では、「1チップで各種のマネジメントIC系の機能を使うことができるため、それらを組み合わせて活用する場合にくらべ、基板面積の削減とBOMコストの低減が図れる。特にBOMコストは欲しい機能はそのままに最大50%の低減が可能となる」と説明する。

同社は過去3年間、順調に成長を続けており、中でもこうした新製品群の販売が四半期ごとで平均28%成長しているという。適用アプリケーション分野は2011年第1四半期の業績では44%が通信機器、31%が産業機器、13%がコンピュータ機器、そして12%がコンシューマとなっている。また、地域別比率は米国が18%、欧州が21%、日本が8%、その他アジアが53%と、アジアが中心市場となっており、「日本は長期にわたりコミットしている地域」とし、自社の成長にとって重要な市場であることを強調する。

また、Mach XO2は富士通セミコンダクター(FSL)の65nm LPプロセスを活用して製造しており、セイコーエプソンの酒田事業所などでも同社製品の製造が行われており、製造面でも日本と親和性が高い。特にFSLの65nm LPプロセスは「ダイサイズが小さく、低コストかつ低消費電力なコスト効率の高い製品を作ることが可能」としており、前世代のMach XO-256(LUT数256)の消費電力30mWに比べ、Mach XO2-256の消費電力は19μWと大幅に引き下げることに成功している。

加えて同社ではコアテクノロジーにフォーカスする方針へと転換を進めており、「開発体制をこれまでの複数拠点での重複した形から、クリティカルな開発を行う米国での2カ所と、それにひも付く形で中国・インドでの開発体制へと変更した。今後、アジアの他の国でも開発を展開させていきたい」としており、低コスト、低消費電力で勝つための方針を強化していくとする。これらの開発チームが、コスト効率の高い65nmプロセス品での開発と次世代プロセス品となる28nmプロセス品の開発を別チームで進める方式を採用しており、将来的な展望に向けたパッケージの開発も進めているという。

65nmプロセスの次が28nmプロセスということについて同氏は、「まずは通信機器向け製品として提供する方針で、その後、ミッドレンジFPGA全体に適用を図ることを計画しており、今後数年以内に複数の製品が登場することとなると思う」としつつ、「65nm LPプロセスは低消費電力、低コストを実現するという意味で成熟したプロセスであり、今後もしばらくは活用することとなる」と65nプロセスも継続して活用していくことを強調する。45/40nmプロセスならびに32nmをスキップして28nmプロセスの活用という意味では、「45nmは我々のイメージするムーアの法則に沿ったものではない」としており、あくまで65nmプロセスと比較して、コストと消費電力を半減させるためには28nmプロセスを活用する必要があるとした。

なお、28nmプロセスを提供できる半導体ベンダ/ファウンドリは限られているが、これについては「どのベンダを選択するかはコストと供給能力。我々に対し、どこまでコミットメントしてもらえるかが重要で、そうした意味ではどこを選択するかは自ずと見えてくる」とした。