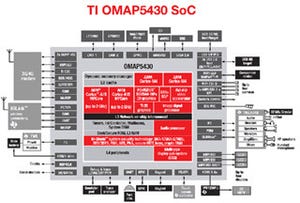

Texas Instruments(TI)とマサチューセッツ工科大学(MIT)は、28nmプロセスで製造するモバイル・アプリケーション・プロセッサの設計手法の詳細に関する共同研究論文を2月20日より米国サンフランシスコで開催されている半導体の国際学会「国際固体素子回路会議(IEEE International Solid-State Circuits Conference:ISSCC 2011)」において発表した。

同DSPは、低電圧動作および28nmプロセスで設計されたシステム・レベルの製品で、モバイル機器において、各種のアプリケーションを実行しながら、従来以上に低消費電力を実現し、電池の動作時間の延長を実現するもの。

高性能(HP)と超低電圧(ULV)プロセスを同時に取り入れるチップ設計では、プロセスのバラつきに影響されずに、定格電源電圧で動作が期待される高電圧性能を犠牲にせず、低電圧機能およびタイミング・クロージャを達成することが求められる。TIとMITは、ULV回路では、低電圧においてチップ内のトランジスタのしきい値電圧のランダムな変動により、チップ上の各回路が動作不良を起こすことがあるが、これを新たに開発したULV設計手法を用いることで、スタンダード・セル・ライブラリとカスタム低電圧動作メモリを開発、0.6Vでの安定した動作を実現した。

また、低電圧における統計的静的遅延解析(SSTA)として、スタンダード・セルの遅延時間の分布は、低電圧では正規分布とはならず、正規分布に基づいた従来のSSTA解析ツール群は、0.6V動作では遅延時間を10~70%少なく見積ることがあった問題を、新たに開発したSSTA手法を取り入れることで、ULVにおける設計タイミングのバラつきを8%以下にまで向上させることに成功した。この、低電圧におけるタイミングを正確に分析する能力により、過剰な設計マージンの設定が不要になるとともに、使用エリアおよび高電圧性能への影響を最少にすることができたという。