パナソニック セミコンダクター社は、Si基板上に形成したGaNパワートランジスタの耐圧を向上させる技術を開発したことを明らかにした。2010年12月6日~8日かけて米サンフランシスコで開催されている半導体デバイスに関する国際学会「IEDM 2010」で発表された。

従来のSi基板上GaNパワートランジスタでは、耐圧は理想的にはGaN膜厚で決まる耐圧と、Si基板の耐圧との和で決定されるが、実際はSi基板の耐圧をトランジスタの耐圧に加えることができなかった。そのため、耐圧向上に向けてはGaN膜厚の増加が必要だったが、Si基板とGaNの格子定数および熱膨張係数の差により発生するクラックのため、GaN膜厚の増加には限界があり、結果としてSi基板上で1,000V以上の耐圧を実現することが困難となっていた。

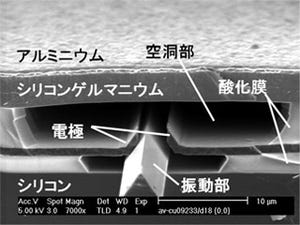

今回、同社の研究チームは、Si基板の耐圧を阻害する原因がSi基板と、GaN層の界面に発生するキャリアによる漏れ電流であることを発見。Si基板表面に選択的にP型層を形成し、耐圧低下の原因となる界面の漏れ電流を阻止した。これにより、Si基板の耐圧をGaN層の耐圧に加えることができるため、耐圧向上が可能となり、同社ではこの技術を「耐圧ブースト(BVB:Blocking Voltage Boosting)構造」と名付けた。

これまで報告されていたSi基板上GaN膜厚の最高値である9μmを適用した場合、耐圧3,940Vの実現が可能で、耐圧をGaN膜厚当たりの値で表した絶縁破壊電界としては、1.9μm時に従来の同一GaN膜厚比5倍となる耐圧2,200V、1,160万V/cm相当と、GaNの材料限界で決まる300万V/cmよりも大きな値を実現できたという。

これにより、Si基板上GaNトランジスタの使用電圧範囲を拡大し、民生機器のモータ駆動用インバータ、各種スイッチング電源に加え、産業用インバータや無停電電源など、GaNパワートランジスタの応用分野がさらに拡がるものと、同社では期待を寄せている。