Alteraは12月6日(米国時間)、2011年に発表を予定している同社の28nmプロセス製品ポートフォリオ向けプロセス技術戦略として、すでに発表済みのハイエンドFPGAファミリにTSMCの28nm High Performance(HP)プロセス技術を適用することに加えて、ローコストおよびミッドレンジ製品ファミリ向けにTSMCの28nm Low-Power(LP)プロセス技術を活用することを発表した。

2つの異なるプロセス技術を採用することにより、カスタマの選択肢を広げ、ニーズに応じて最適化されたデバイスを提供できると同社では説明しており、これにより、28nm LPプロセス製品では、オートモーティブや産業機器をはじめとする市場セグメントにおけるコストおよび消費電力重視のアプリケーションに対して、コストと消費電力を低減することが可能になるほか、ミッドレンジクラスの製品ファミリにおいても、コストと性能と消費電力の最適なバランスを提供することが可能になるという。

一方、28nm HPプロセス技術は、ハイエンド・アプリケーションで求められるコア性能およびトランシーバ性能に必要な技術で、次世代100G/400Gシステムの開発を担う 28Gbpsトランシーバなどの機能を統合することで、ハイエンドFPGAの性能を向上させることを可能とする。

また、28nm HPプロセス技術を採用したFPGA製品は、高性能コンピューティングや軍用機器、ワイヤライン・システムなどのアプリケーションをターゲットとしており、同社では28nm LPプロセスと28nm HPプロセスの両方を採用した製品ポートフォリオとすることで、ハイエンド、ミッドレンジ、ローコストすべての市場セグメントにおいて、より多くのASIC、ASSPに対する市場機会に対応することが可能となり、組み込みプロセッサソリューションと組み合わせることで、より多くのDSPやマイクロプロセッサを28nm FPGAに置き換えることが可能になるとしている。

このほか、同社では併せてCPLD製品の新ファミリ「MAX V」を発表した。すでに一部量産出荷を開始しており、最初の2つのMAX Vデバイスである「EP5M80ZE64C5N」および「EP5M240ZT100C5N」の販売単価はそれぞれ100個あたり1.70ドル、4.90ドルとなっている。その他のMAX Vファミリについても、2011年第2四半期末までに量産出荷が開始される予定となっている。

同ファミリは、インスタント・オン機能、1チップ、不揮発性という従来からのMAX シリーズの特長を維持しつつ、トータル消費電力を同等の集積度を持つ競合製品と比べて最大50%低減することに成功したもので、40~2,210ロジックエレメント(LE)の7つの製品ラインアップが用意されている。

また、45μWのスタティック消費電力によるバッテリ寿命の延長など、消費電力の低減を実現しているほか、競合CPLD製品比で、同一コスト条件で単位面積あたり、より多くのI/Oとロジックを提供することに成功。これにより、設計者はコスト目標の達成をより簡便に行うことが可能となると同社では説明している。

さらに全MAX Vファミリ製品は、環境基準に対応した、ハロゲン・フリーの各種パッケージ(EQFP、TQFP、FBGA、MBGA)で提供され、アナログ制御やI/O拡張、インタフェースブリッジング、電力管理などの用途に応じた使い分けが可能となっている。

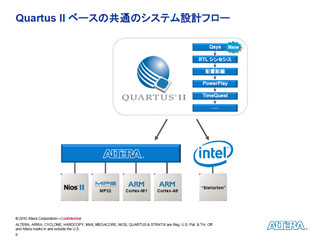

なお同社は、これらの発表に併せて、同社のFPGA/CPLD開発ソフトウェア「Quartus II」の最新バージョンとなる「Quartus II v10.1」も発表している。サブスクリプション・エディション v10.1には、FPGAに最適化されたネットワーク・オンチップ・ベース・インタコネクトを備えた同社の次世代システム統合ツール「Qsys」のベータ版が含まれている。Qsysは、メモリマップドおよびストリーミング・インタフェースをサポートし、同社のSOPC Builderツールの2倍近い性能で、大規模FPGAデザインのシステム拡張性を高めることが可能となるほか、業界標準インタフェース(Avalon)やARMのAMBAやAXI、AHBなどのサポートを可能としている。

また、階層構造デザイン・フローにより、多数のIPやシステムコンポーネントが組み込まれたシステムの設計において、FPGAを複数のサブシステムに分割して取り扱うことで、システムのスケーラビリティを高めることが可能だ。これにより、各サブシステムの管理を容易化できるとともに、システム性能への影響も最小限に抑えつつ、サブシステムを新たに追加することも可能になると同社では説明している。