Freescale Semiconductorは、データ・パス・アクセラレーション・アーキテクチャ(DPAA)プログラミング・モデルを搭載した同社の通信プロセッサ「QorIQ」として「P1023」「P1017」「P2040」を発表した。P1023およびP1017は2011年第1四半期のサンプル出荷、P2040のアルファ・サンプルも2011年第1四半期の出荷が予定されている。

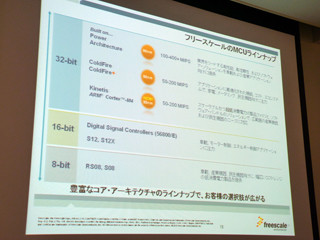

これにより同社のDPAA技術は、400MHz~2.2GHzの周波数範囲で1コア~8コアのすべてのQorIQプラットフォーム・レベルへと拡充されたこととなる。

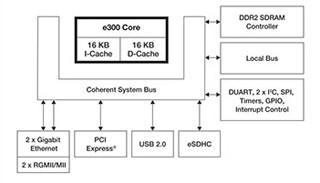

3製品ともに45nm SOIプロセスを採用。P1023およびP1017はe500コアを採用し、最大800MHzで駆動、P2040はe500mcコアを採用し、1.2GHzで駆動する。いずれもDDR3/3L SDRAMメモリ・コントローラを搭載しているほか、P2040は1MBの共有CoreNetプラットフォーム・キャッシュも搭載している。

またユーザーは、標準的なDPAAソフトウェア・アーキテクチャで1つのQorIQプロセッサ向けのコードを開発すれば、それを機能拡張または機能縮小してQorIQファミリの全プラットフォーム間で利用することが可能となり、開発サイクルの短縮が可能となるほか、幅広い価格帯および性能範囲をカバーする最終製品を開発することができるようになる。

P1023とP1017は、2コアおよび1コアのデバイスで、802.1n対応のワイヤレスLANアクセス・ポイントやSMBゲートウェイ、低価格ルータなどを想定している。主な特長は、パワー・オーバー・イーサネットを実現する低消費電力、3種類の無線ソリューションに対応する3つのPCI Expressコントローラ、エンタープライズWLANアクセス・ポイントの性能を最適化するデータパス・オフロード、および暗号化アルゴリズムのプロトコル処理の負荷軽減などとなっている。

P2040は、コストおよび消費電力が最適化された4コア・デバイスで、ルータ、LTEチャネル・カード、およびエンタープライズ・セキュリティ・アプリケーションなどに向けたソリューション。一般的なパケット処理タスクの負荷を軽減するDPAAの採用に加えて、柔軟なSerDes構成のサポートにより、必要なグルー・ロジックが最小限に抑えられているほか、組み込みハイパーバイザ技術により各コアごとに独立したオペレーティング・システムの稼働が可能であるため、真の意味でのハードウェアの分割および仮想化が実現しすることとなる。

QorIQ DPAAは、メイン処理コアから所定タスクの負荷を軽減するため、各コアは低周波数、低コスト、および低消費電力で、より重要なタスクの実行やアプリケーションの性能目標を達成することができる。DPAAを構成するブロックは、Ethernetポート上のポリシング、クラシフィケーション、およびスケジューリングを実装するフレーム・マネージャとキューイング、輻輳制御、ワークロード配分、パケット・オーダリングを実行するキュー・マネージャ、パケットをバッファに割り当ててメモリ消費を最小限に抑えるバッファ・マネージャ、暗号化アルゴリズムを実装するセキュリティ・ブロック、および統合脅威管理など向けにパケット内のテキスト文字列の検索を実行するパターン・マッチング・エンジンとなっている。

また、同社は、DPAAにアクセスするためのアプリケーション・プログラミング・インタフェース(API)を用意しているほか、標準的なGUIベースの構成ツールおよびDPAA構造を設定するためのサンプルのフレームワーク・アプリケーションも提供している。