Intelは50Gbpsの転送速度を持つ光伝送回路が実現したことを発表したが、この発表に先立ち電話会議の形で詳細が公開された。そこでこの発表の詳細をご紹介したい。

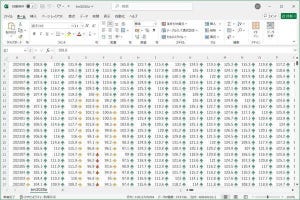

今回Intelが発表したのは、50Gbpsの速度を持つシリコン光リンクの一式である(Photo01)。従来からIntelはSilicon Photonicsに力を入れてきており、コンポーネントレベルでは色々と成果が上がっている、という話はたとえばこのあたりからの話を読んでいただくのが早いが、これまではあくまでリンクを構成するためのコンポーネントレベルに留まっていた(Photo02)。

例外だったのが、2010年北京で発表されたLightPeakである。これは一応製品化を念頭に置いたコンポーネントである。ではLightPeakと今回の発表の最大の違いは?というと、多重化である。LightPeakは送受信それぞれ1chの光回路で実現されており、それぞれ10Gbpsのスピードとなっている。これに対し、今回は12.5Gbpsの光回路を4本束ねて50Gbpsを実現した形だ。この「束ねる」機能について、一応の実用化の目処が立ったという形だ(Photo03)。

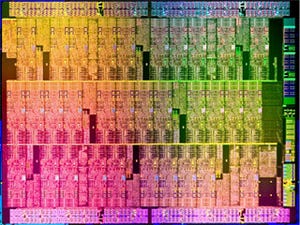

以前このあたりでも指摘した話であるが、いくらSilicon Laserだからといっても、一波長あたりの信号速度をむやみやたらと上げることはできない。Photo02にもあるように、現時点で実験室レベルでは40Gbpsまでの送受信が可能であるが、量産のレベルではLightPeakが当初10Gbpsを狙っていることからも判るとおり、まだそれほど高速な動作は見込めない。なので多重化は必須であり、しかしながらそのために必要なMultiplexer/Demultiplexerをシリコンで作りこむことに関してこれまでは一切アナウンスが無かった。これに関して今回は、4波長のMultiplexer(Photo04)とDemultiplexer(Photo05)をシリコンで一体的に組み込んだ形でTransmitter/Receiverの製造に成功したことが最大の発表と言ってよい。

|

|

|

|

Photo04:細かく言えば、4波長のHybrid Laserを4つまとめて組み込んだことも大きな特徴と言えるだろう。詳しくは後述 |

Photo05:実際のチップの大きさはPhoto03参照。TransmitterはHybrid LaserのLaser Sourceを組み込んでいる分長くなるのは致し方ないとして、Receiver側もそれなりにDemultiplexerが大きい模様だ |

ちなみにLight Peakではコネクタ内部にPHYを組み込むという形でコネクタの精度を確保しているが、今回の発表では光コネクタは純粋にPasssive connectorとなっている(Photo06)のも目をひくところだ。

|

|

|

Photo06:PCで使われるFR-4ベースの実装で利用できるようにする、というのが目標だったそうである。それにしてもガイドピン(写真で言うところのAlignment Pin)はあまり強度が無さそうで、量産レベルではまだ問題がありそうな気もする |

ところで今回、どうMultiplexer/Demultiplexerを実現したかに関する説明は無かったのだが、その推定のヒントが示された(Photo07)。まず送信側で言えば、それぞれのレーザーの特性をうまく調整することで、ほぼ20nmごとに4つのレーザー光が分離されているのが判る(Photo08)。問題は受信側の方で、4つの波長をうまく分離できるようなBPFが構成されている(Photo09)。ここから考えると、今回のMultiplexerは図1、Demultiplexerは図2の様な構造になっていると考えられる。ベースになるのは恐らく2入力(4入力かもしれないが)の光混合/分配回路であろう。これをシリコンで実現できれば、Multiplexerは簡単に構成可能である。

問題はDemultiplexerの方である。プリズムなどを使えば、波長別に光信号を綺麗に分離できるが、20nmの波長の差できちんと分けられるプリズムを作るのは容易ではないし、Siliconベースでこれを作るのはさらに難しくなる。そこでDemultiplexerは単なる光分配回路として構成し、その先でFilterを掛けることで望む光信号を選別する形で実装されたようだ。Photo09のグラフは、図2のFilter #1~#4の特性図と考えれば理解が早い。

この場合の最大の問題は、分配に応じて光信号が減衰することだ。ざっくり言ってPhotodetectorに届く光信号の強度は、送り出したときの4分の1でしかない。なので送受信をしっかり行うためには

- Hybrid Laserの出力を上げる

- Photdetectorの感度を上げる

のどちらかもしくは両方の対応が必要になる。もっとも出力を上げると消費電力も増えるわけで、なのでPhotodetectorの感度を上げるのがまずは最初に行うべき事となるだろう。

ちなみに今後の展開としては、Modulatorの速度を上げるほか、より多重化を増やす形で将来的には1Tbit以上のLinkを可能にする(Photo10)という壮大な目標が掲げられているが、x25という事は信号強度が25分の1になるという話であり、より高出力なレーザーや高感度なPhotodetectorが必要になる事になる。ただそれでも、これまでは空絵事でしかなかったシリコンベースのMUX/DEMUXが実現できたことで、こうした目標も空絵事から「実現に困難はあるが、理論上は可能」なものに進化したことは素直に喜ばしいと判断すべきであろう。ちなみに今回の発表はあくまで研究目的のもので、製品化には3~5年先であろうとされているが、Primary TargerはサーバやHPCなどとしつつもこんな図(Photo11)が出てくるあたり、将来のLightPeakを睨んだものになると考えてもいいのかもしれない。

|

|

|

|

Photo10:これそのものは以前も示されていたものである |

Photo11:サーバなどのモジュール間接続は前から言われているもの。Multi-terabyte Memory Bankの"Memory"が何なのかがいまいちわからないが、Flash Memoryあたりを想定すれば、これはLightPeakで共有SSDをぶら下げていると見做すことも出来る。実際LightPeakは当初は10Gbpsを狙うが、将来的には100Gbpsまでスケールするとしており、今回のテクノロジが利用される可能性は高そうだ |