東京大学(東大)大学院工学系研究科 竹内健准教授らのグループは、半導体理工学センター(STARC)と共同でPCや携帯電話などに使われる集積回路の0.5V動作に向けた低コストSRAM技術を開発したことを発表した。同技術の詳細は、2010年6月15~17日に米国ハワイ州で開催される半導体デバイスに関する国際会議「VLSI技術シンポジウム(2010 Symposium on VLSI Technology)」にて16日(現地時間)に発表された。

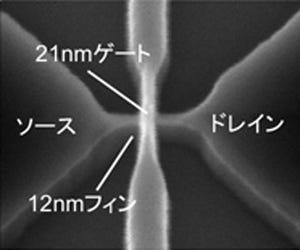

低電圧動作SRAMセルにおいてデータの入出力を行うパスゲートトランジスタは、データを読み出す際に流せる電流を少なくする必要があるが、書き込む際は多くする必要があるという矛盾した要求を突きつけられている。

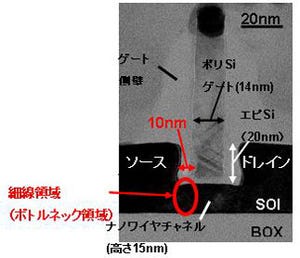

この矛盾を解決しようとするとパスゲートトランジスタを非対称にする必要があるが、従来の解決方法では追加の不純物導入工程により製造コストが上がってしまう課題があった。そこで同研究グループでは、製造工程後にパスゲートトランジスタの絶縁膜中に局所的に電子を注入することでパスゲートトランジスタを非対称にし、この課題を解決することに成功した。

電子注入は特定の電圧を製造工程後にすべてのSRAMに同時に与えるだけの簡単なもので、高価な製造工程の追加が不要だ。

また、同技術では製造工程でトランジスタの特性がバラつくためにSRAMセルの安定性のバランスが崩れる問題も、電子注入を行うことで自己修復させることが可能となる。

同技術を用いた場合、SRAMの動作マージンは従来技術比で70%改善し、0.5Vの低電圧動作の実現も視野に入ってきたという。0.5V駆動が実現されれば、現在の集積回路の消費電力を1/10まで低減できる可能性が出てくることとなり、より環境にやさしいグリーンデバイスが実現できることとなる。