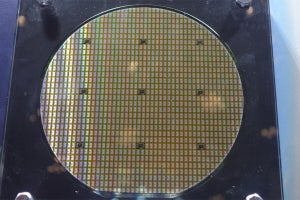

Taiwan Semiconductor Manufacturing(TSMC)は、SoCの配線後のロジックブロック面積を、従来のスタンダードセル・ライブラリ比で15%削減することが可能となるスリム・ライブラリを発表した。

同ライブラリは、同社の65nm LPプロセスを対象としており、既存の実装フローに適合している。そのため半導体設計者は、設計ツールや実装手法を変更することなく、既存設計あるいは新規の設計に、同ライブラリを使用することができる。

同ライブラリは、TSMCとTela Innovationsが共同で行った、設計およびプロセス最適化プログラムである「AreaTrim」の成果で、Telaの特許に基づいたレイアウトスタイルと、TSMCのプロセス最適化に基づいて作られている。両社では、さまざまなマイクロプロセッサコアを用いて、合成およびタイミングドリブン配置配線により、15%の面積削減を実現したという。

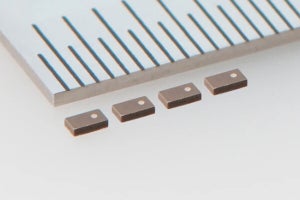

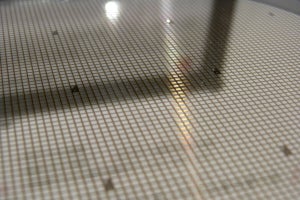

レイアウトスタイルは、面積削減のために、固定ピッチと一定方向に並べたポリによる均一な密度と、改善された製造プロセス制御により実現したリソグラフィ最適化パターンによって描かれており、結果として同ライブラリは、mm2あたり最大100万ゲートのゲート密度を達成している。

また、従来の9トラック構成から8トラック構成に再設計されているが、従来と同等の性能と電力を実現しており、キャラクタリゼーション・コーナー一式とともに、複数のVt(しきい値)オプションとパワーマネージメントセルが含まれている。

なお、同ライブラリはすでに一部のカスタマに提供が開始されており、希望する場合は、直接同社まで問い合わせるか、TSMC Onlineのカスタマデザインポータルにアクセスするように、と同社ではコメントしており、正式リリースは2011年第1四半期からを予定している。