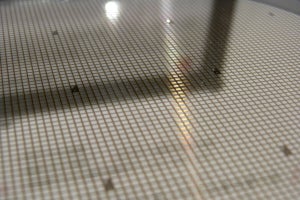

National Semiconductor(NS)は、ゼロレイテンシ双方向制御チャネル内蔵チャネルリンクIIIシリアライザ/デシリアライザ(SerDes)ファミリを発表した。

同SerDesは1本のツイスト・ペア上で高速クロック・データと低速双方向I2C制御バスを提供することが可能。これにより、産業用ビデオ/画像処理/ディスプレイ・アプリケーションで、従来ソリューション比最大50%のインターコネクト・サイズ、重さ、コストの低減を実現することが可能となる。

同ファミリは2つのデバイスから構成されており、1つはシリアライザ「DS92LX2121」とデシリアライザ「DS92LX2122」の組み合わせで、18ビット・カラーのディスプレイ・アプリケーションまたは最大1050Mbpsのデータ・リンクを駆動することが可能だ。

また、シリアライザ「DS92LX1621」とデシリアライザ「DS92LX1622」の組み合わせでは、最大800Mbpsの16ビット・データを駆動させることが可能だ。いずれのチップセットもロー・ボルテージCMOS(LVCMOS)パラレル・インタフェースを採用しており、10MHzから50MHzで動作することが可能。

いずれもチップセットもサンプル出荷を開始しており、量産品は2010年7月から供給する予定となっている。単価は、1,000個一括購入時でDS92LX2121(40ピンのLLPパッケージ)とDS92LX2122(48ピンのLLPパッケージ)がそれぞれ5.30ドル、DS92LX1621(32ピンのLLPパッケージ)とDS92LX1622(40ピンのLLPパッケージ)がそれぞれ5.10ドルとなっている。

また、同社は併せて、一般アプリケーション向けに双方向の制御チャネルがない2つのチップセットを「チャネルリンクIIファミリ」として発表している。1つはシリアライザ「DS92LV2421」とデシリアライザ「DS92LV2422」で、LVCMOSパラレル・インタフェースを採用している。もう1つはシリアライザ「DS92LV0421」とデシリアライザ「DS92LV0422」で、チャネルリンクSerDesで使用されている小振幅差動信号(LVDS)インタフェースを採用している。このため、DS92LV0421/DS92LV0422はLVDSブリッジ機能を通じて、チャネルリンクSerDesからのアップグレード・パスを提供する。いずれのチップセットも高速データとクロックを組み込み、24ビット・データを最大1.8Gbpsの転送レートで駆動し、10MHzから75MHzで動作することが可能だ。

今回発表されたチャネルリンクIIIおよびチャネルリンクIIチップセットはいずれも、シグナル・コンディショニング機能を内蔵しており、リモート・ディスプレイまでの高速信号の駆動距離を他の一般的なSerDesの2倍に延長することが可能だ。また、産業用アプリケーションの過酷な動作環境でEMI(電磁波障害)を低減するための拡散スペクトル・クロッキングを備えているほか、8kV超のHBM(人体モデル)ESD(静電気放電)耐量を提供、ISO 10605のESD規格に準拠している。さらに、いずれのSerDesファミリも-40℃から+85℃で動作し、リンク整合性を検証するための内蔵自己テスト(BIST)診断機能を備えている。

なお、今回発表されたチャネルリンクIIチップセットもすでにサンプル出荷を開始しており、2010年7月からの量産開始を予定している。サンプル価格は、1,000個一括購入時でDS92LV2421(48ピンのLLPパッケージ)とDS92LV2422(60ピンのLLPパッケージ)がそれぞれ5.95ドル、DS92LV0421(6ピンのLLPパッケージ)とDS92LV0422(48ピンのLLPパッケージ)がそれぞれ6.25ドルとなっており、5MHzから50MHzの低速グレード品もリリース予定となっている。