STMicroelectronicsは、Network Application向けに32nmプロセスを使ったASICプロセスが利用可能になったことを発表した。これは同社の32LPH(Low-Power High-performance)プロセス上に構築した32nm SoCプラットフォームを核としたもので、32nmのバルクCMOS上にSerDes IPを組み合わせたものである。

この新しい32LPH上で利用できるASICデザインプラットフォームは200mm2を超えるような巨大なASICデザインを可能としており、機能ブロックを分割しながら高性能/高機能と低消費電力/省サイズを同時に実現できるものとなる。特にこれはエンタープライズ向けスイッチやルータ、あるいはファイバや無線の混在した環境におけるインフラといった、次世代ネットワーク向け高性能アプリケーション向けASICのデザインに効果的であると同社は述べている。

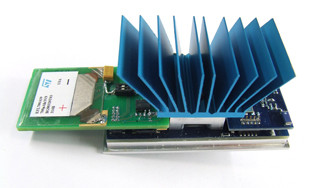

この32LPHにおけるキーとなるのが、S12と呼ばれる同社のSerDes IPである。これはすでに特定のカスタマ向けに、実験室レベルでのデモも成功している。特にNetwor Application向けASICにとってS12はキーとなるもので、チップ間接続やチップ/モジュール/バックプレーンの接続に欠かせない要素であるとしている。

32LPHは最大10層の配線層を利用可能であり、ベースはISDAアライアンスにしたがった32nm High-K/メタルゲート(HKMG)を利用している。ただし、10Mbit/mm2の密度のembedded DRAMやTCAM(Ternary Content Address Memory)といった特定のIPや周辺回路は同社が独自に提供するものである。

またS12 SerDesIPは1マクロあたり最大で8chの12.5Gbitの送受信が可能である。S12はオプションとして提供されるフリップチップBGAパッケージを前提にデザインされており、また同社はまもなく転送速度を14Gbpsに引き上げたS14 SerDes IPの提供も予定している。

この32LPHプロセスを使った最初のASICプロトタイプは2011年の初頭に予定されており、量産が立ち上がるのは2011年後半とされている。