産業技術総合研究所(産総研)は、1Gビット以上の大容量のスピン注入型磁気抵抗ランダムアクセスメモリ(スピンRAM)を実現することが可能となる垂直磁化トンネル磁気抵抗(TMR)素子を開発したことを発表した。

産総研は、2008年に東芝らと共同で、垂直磁化TMR素子をベースとしたスピンRAMの試作に成功、Gビット級のスピンRAMに必用な記録保持性能と低い書き込み電流値の両立が可能だということを原理的に示していた。しかし、実際のメモリとして活用するためには、読み出し性能の向上が課題として残されていた。

読み出し性能の向上には、大きな出力信号を得るための高い磁気抵抗(MR)比だけでなく、周辺回路とのインピーダンス整合のための低い素子抵抗(RA)の両方を併せ持つ素子の開発が必要とされている。このため、産総研では、1Gビットの容量実現に必要とされる読み出し性能として、単位面積で規格化したRA値を30Ωμm2以下、信号強度に対応するMR比を50以上とすることを目標に研究を行ってきた。

開発のポイントは以下の2つ。

- TMR素子を構成する超薄膜を平坦化する技術の開発

- 高いスピン分極を誘起する界面層の開発

これらのポイントを満たすため、新たに開発された垂直磁化TMR素子は、垂直磁化電極層-1がテルビウム鉄コバルト(TbFeCo)層と界面層、垂直磁化電極層-2がコバルト/白金(Co/Pt)積層と界面層で構成され、互いが基板面に対して垂直方向に磁化する。垂直磁化電極層-1と垂直磁化電極層-2の磁化の向きが同方向か、逆方向かにより、電気抵抗が変化し、それによって0もしくは1の情報を記憶することができる。

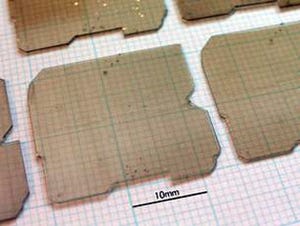

目標値である30Ωμm2以下のRA値を実現するためには、トンネルバリアとして用いる酸化マグネシウム(MgO)層の厚さを、原子層で5層程度の1.3nm程度以下に薄くすることが必要だが、新たに原子レベルで平坦化する薄膜作製プロセスを開発、これにより原子レベルで平坦な表面の垂直磁化電極層-2、および、極薄かつ均一な膜厚(1nm)のトンネルバリア層(MgO層)の形成に成功し、垂直磁化TMR素子のRA値として約4Ωμm2を実現した。

また、界面層材料として、結晶性のコバルト鉄(CoFe)合金とアモルファス合金であるコバルト鉄ボロン(CoFeB)合金を組み合わせた界面層を新規に開発。CoFeBのみで構成される界面層へCoFeを導入することで、アモルファス層の結晶化を促進させることが可能となり、結果として、低RA値(約4Ωμm2)ながら85%のMR比を実現した。

これらの値は、目標値を上回るもので、1Gビットの容量はもちろんのこと、5Gビット以上の回路設計も可能となったという。

なお、今回の成果について産総研では、他の材料・結晶配向を持つ垂直磁化膜層にも適用可能であり、幅広い応用の可能性があるとしており、今後は、今回の技術をベースにさらに高いMR比の実現に向けた開発を進め、大容量スピンRAMの量産化技術の確立を目指すとしている。