FPGAベンダ大手のXilinxは5月3日(米国時間)、同社のFPGA開発環境「ISE Design Suite 12」の第1弾となるバージョン12.1を発表した。ロジック設計向けの「LOGIC EDITION」、エンベデッド・デザイン・ソリューションの「EMBEDDED EDITIN」、DSPシステム向け「DSP EDITION」の3種類が主なデザインツールとして提供されており、すでに購入が可能となっている。また、すべての機能が30日間限定で利用することが可能な評価版も同社Webサイトにて無料でダウンロードすることが可能だ。

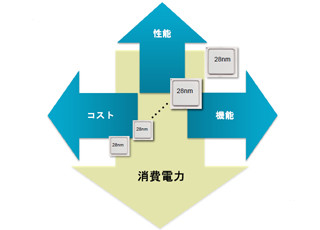

ISE 12には、新機能として自動クロックゲーティング技術を搭載。これにより、アルゴリズムが論理方程式を分析、個々のクロックサイクルの結果に影響を与えないソーシングレジスタの検出や該当するサイクルにクロックイネーブルを生成して活用を抑止することで、エンジニアが出したい出力波形を自動的にチェックし、出力に影響がなく、かつシンプルなパターンを形成することで、ダイナミック消費電力を最大30%削減することが可能となる。

また、デザイン保存機能により、フロアの一部分だけを変更しても全体の配置配線を変更することなく、変更したモジュールのみ検証することが可能となったほか、第4世代のパーシャルリコンフィギュレーション技術の採用により、これまでユーザが手動で行っていた作業を通常のデザイン作業の中に含むことが可能となり、スタティックでリコンフィギュレーション可能なパーティションの定義、ハードウェアリソースを分離するためのフロアプラン、個々のデザインコンフィギュレーションの配置とルーティングの決定、完全なビットファイルとパーシャルビットファイルの作成を通じた直感的な活用が可能となった。

加えて、同社はARMと共同でAXI4の仕様策定に関与しており、これによりISE 12ではAXI4 IPのサポートが可能となる。このため、AXI4に準拠したIPを活用することで、設計リソースの低減や開発期間の短縮などが可能となるとしており、2010年秋以降、DSPやエンベデッド、コネクティビティなどのIPのサポートを進めていく予定。

なお、ISE 12については、2010年夏にVirtex-6を用いたデザイン向けパーシャルリコンフィギュレーション機能を搭載、ならびにSpartanー6向けにインテリジェントクロックゲーティングをサポートしたバージョン12.2を、またAXI4対応の各種IPのサポートをしたバージョン12.3を同秋にそれぞれリリースする予定としている。