NECは2月10日、LSIの性能劣化の進行度を自律的に監視するディペンダブル技術を用いて電圧制御を行うことで、次世代システムLSIの消費電力を最大で1/2に低減できる、基本回路技術を開発したことを発表した。米国にて2月7日より開催されている半導体の国際学会「ISSCC(The International Solid-State Circuits Conference)」において、2月9日(現地時間)に発表された。

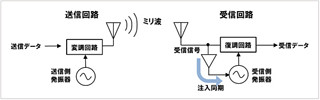

今回開発した技術は、LSIの電圧を細かく制御して不要な電力消費をおさえるとともに、小型・高精度なセンサでLSIの劣化度を監視し高信頼性を実現するもの。

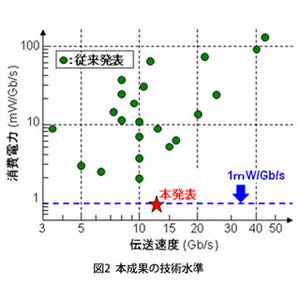

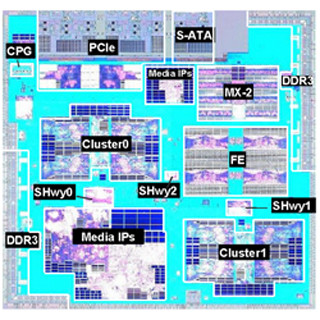

具体的には、LSI内に分かれている部位ごとにその劣化の進行度を監視し、進行度に応じて電源電圧およびトランジスタのしきい値電圧などを細かく制御する手法を開発。これにより、LSIの性能確保のために全回路一律に電圧を上げることが不要となり、従来比最大約半分の消費電力で動作を実現した。

また、経年劣化の進行度合いに応じて遅延時間が変わる小型センサ回路を繰り返し動作させ、その遅延時間を測定する技術を開発。同センサは、回路面積を従来の約1/7に小型化したため、LSI内部により多くのセンサ回路を埋め込むことが可能になり、LSI内の部位ごとの劣化監視を行うことが可能となった。

さらに、経年劣化の度合いの測定では、高精度な測定を実現するために、従来よりも約10倍速い時間刻みでの測定が可能な回路技術を開発。これにより、例えば、ごく短い時間(1μs以下)でも遅延劣化を引き起こし、従来は発見が困難だったNBTI(Negative Bias Temperature Instability)劣化も見落とさずに監視することが可能となった。

なお、同社では、今回開発した技術を、システムの低電力性能と長期高信頼性能の両立を実現するものであり、今後もディペンダブルLSIの研究をより進めていくことで性能向上を図っていくとしている。