日立製作所は2月9日、1Gbpsあたり1mW以下の消費電力で駆動するトランシーバ回路(SerDes)の開発に成功したことを発表した。同技術の詳細は、米国にて2月7日より開催されている半導体の国際学会「ISSCC(The International Solid-State Circuits Conference)」において2月10日(現地時間)に発表される予定

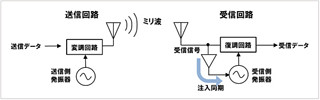

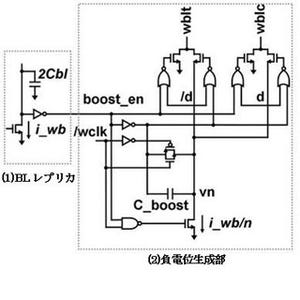

同研究は同社が総務省および情報通信研究機構(NICT)の支援を受けて行ったもので、100Gビットイーサネット(100GbE)向けに伝送速度12.5Gbpsのトランシーバ回路を考案した。今回、定常電流を削減する回路技術(電圧電流モード併用出力回路)と、従来のトランシーバ回路では2系統を必要としたクロックを1系統に削減する回路技術(単相クロック位相比較回路)を開発したことで、性能を維持しつつ低消費電力を実現した。

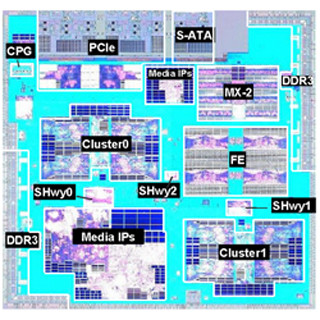

また、65nm CMOSプロセスを用いたトランシーバ回路を試作し動作検証を行ったところ、伝送速度12.5Gbpsで100GbE仕様となるビット誤り率10-12の双方向通信を、消費電力12.3mWで行うことができることが確認された。これは、1Gbpsあたりに直すと0.98mWの消費電力であり、乾電池や太陽電池を電源とした場合においても、安定した連続動作が可能なことも確認したという。

なお同社では、今回試作したトランシーバ回路は、100GbEnoほか、サーバやルータなどの情報処理装置内のLSI間の信号伝送への適用も見込めるほか、携帯機器向けLSIへの適用もできることから、幅広いIT機器の低消費電力化に寄与する可能性があるとしている。