東芝は2月8日、低電圧LSIの実現に向け、低電圧化でボトルネックとなるSRAMの動作不良を防ぐ回路技術を開発、32nmプロセスを採用した試作LSIでのSRAM不良率を0.7V時で、従来比1/10,000に低減したことを明らかにした。同技術の詳細は米国にて2月7日より開催されている半導体の国際学会「ISSCC(The International Solid-State Circuits Conference)」において、2月10日(現地時間)に発表される予定。

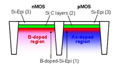

LSIの低電圧化は機器の消費電力削減には有効な手段だが、プロセスの微細化によりチップ上に形成されるSRAMの特性バラつきが無視できないレベルとなり、結果として誤作動などを引き起こすため、その対策が求められていた。

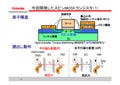

今回、東芝では、低電圧SRAMの性能向上技術として知られている動作アシスト技術(リードアシスト/ライトアシスト技術)の実用性を高めた新方式を採用し、不良率の低減に成功した。

動作アシストは、SRAMの読み書き時にビット線とワード線の電位を下げて動作マージンを広げる手法だが、SRAMの容量やセル配列に応じ、負電位生成回路を構成するキャパシタの素子パラメータの調整が必要となるため、設計効率が低下し、実用化の障壁となっていた。

東芝では、ビット線のレプリカを設置。セル配列の寄生容量値をモニタし、それに応じて負電位生成の動作を最適化する手法を開発、採用することで、素子パラメータの調整を不要とし、メモリ容量やセル配列に応じたSRAM設計データをソフトウェアで生成することを可能とした。また、同技術では素子数は変えておらず、そのため、セル面積は従来と比べても増加はない。

|

|

|

今回開発された技術を用いた回路構成。(1)のBL(ビット線)レプリカの長さに応じて、(2)の負電位生成部の動作タイミングを自動的に決める仕組みを導入、個別の素子パラメータ調整を不要にした。これにより、メモリ容量やセル配列に応じたSRAM設計データをソフトウェアで簡便に生成できるようになった |

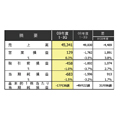

これらを用いた32nmプロセスの試作LSIは、電源電圧を通常比30%減の0.7Vにした時のSRAM不良率が前述のとおり従来比で1/10,000であり、東芝では、同技術を含めた低電圧LSI技術の開発をさらに進めていくことで、プロセスの微細化による高性能化と低電圧動作による低消費電力化を両立したLSIの早期実現を目指していくとしている。