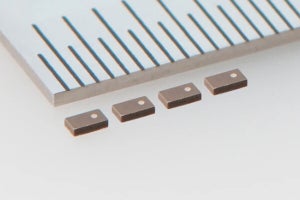

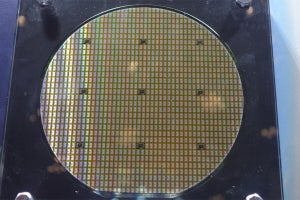

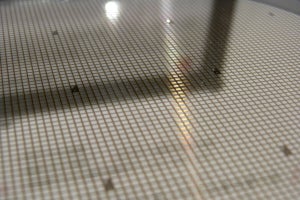

イー・シャトルは、富士通マイクロエレクトロニクス(FML)およびアドバンテストと共同で、電子ビーム直接描画(EB直描)技術を、従来のホール層(ビア)の形成用に加え、配線層にも適用することに成功したことを明らかにした。また、これに伴い、同技術を活用した90nmおよび65nmプロセスのLSI試作サービスを開始したことも併せて発表した。

|

|

|

イー・シャトルの代表取締役社長である日野陽司氏 |

これまでイー・シャトルでは、アドバンテストのEB直描装置「F3000」を活用し、2008年3月から65nmプロセスのLSI試作サービスを提供してきたが、こうした取り組みにより「EB直描を活用する市場があることや、先端プロセスのLSI製造にもEB直描が適用可能なことが実証できた」(同社の代表取締役社長である日野陽司氏)とするほか、「最先端プロセスを採用するLSIにおける量産などにも、より強力なEB直描装置の並列化により対応することが可能という道筋が示された」(同)と説明する。

先端プロセスでのLSI設計での課題は、マスクコストとOPCなどの回路設計コストおよびそれらの製造にかかる時間の増大。特にマスクコストは45nmプロセスで数億円規模となっており、簡単にいくつものLSIを設計・製造するわけにはいかなくなっている。

|

|

|

|

プロセスの微細化と回路規模の肥大によりマスクコストは急騰。単純計算だが、仮に1億円でマスクを作った場合、1000円のデバイスを10万個売ってようやくマスク代(1億円)に到達する。そのほかにもデバイスの開発・製造には材料費や開発コスト、人件費などが含まれることとなるため、コスト削減を図る必要がでてくる |

|

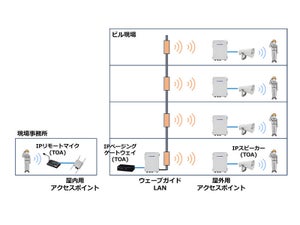

こうした状況に対応するために考案されたのがEB直描であり、同社ではパターンを矩形の組み合わせと登録されたパターンで描画するCP(Character Projection)法を採用することで、マスクやレチクルを不要にしたほか、直接EBで描画するため、OPCなどの複雑な処理をしないでパターン形成を実現することを実現した。「唯一とも言える問題は、膨大なパターンを歩留まり良く露光できるかどうかであるが、これは"F3000"と当社の技術を組み合わせたシャトルサービスなどの実績などですでに実証された」(同)とし、シャトルサービスとして多くの企業や大学などが活用してきた実績を強調する。

ただし、現在のスループットは1.3wph程度であり、「その速度では、研究開発やLSIの試作、初期サンプルの製造といった少量生産の市場に限定され、市場規模としても100億円程度」(同)としており、さらなるスループットの向上として、マルチビーム方式のEBを用いたMulti Column Cells(MCC)の量産システムの開発をアドバンテストと進めていく方針。

マルチビームは文字通り、複数のEBを同時に照射することで1本のEBで描くのに比べて描画速度を増す技術。また、MCCは、例えばビーム本数132本で10wphのスループットを持つユニットを10クラスタ、EB直描装置の中に搭載することで合計で100wphのスループットを確保しようという考え。EBは1本だと、300mmウェハの端から端までステージを動かすために広いスペースを確保する必要があるが、マルチビームになれば、端から端までステージを動かす必要がなくなる分、チャンバそのものの小型化が可能となるため、EUV露光装置と同程度のサイズで同程度のスループットを確保することが可能となる。

|

|

|

|

EB直描では、ビームでパターンを形成していくため、1本だけのビームでは非常に時間がかかる。それを本数を増やすことで短縮するのがマルチビームによる並列処理(MCC) |

10wphのMCCを10クラスタ搭載することでEUVとほぼ同等のフットプリントを実現した100wphのEB直描装置が可能となるという |

また、従来の露光装置と比べて気になるのが位置合わせ精度(重ね合わせ精度)や歩留まりの問題。同社がこれまで行ってきた中で得られたデータでは、重ね合わせ精度や線幅のバラつきなどはArFの露光装置と同等以上を達成しており、歩留まりも条件によって異なるが、おおむね90%以上を達成しているという。

|

|

|

|

重ね合わせ精度などはArFと遜色はない。また、大きな開口部に囲まれた部分のコントラスト低下などの問題がEB直描で生じるが、独自のコントラスト改善技術などを取り入れることで、それらの問題を解決したという |

|

加えてコスト面としては、「すべての配線層のファインレイヤをEBに置き換えた場合、65nmプロセスでは50%以上のレチクルコスト削減が可能となる」(同)ことを強調する。また、今後の方向としては、45nmでの配線層やバルク(素子形成)層形成にもめどが立っており、「最初のアイランドの時点で、即座に製造に入ることが可能となるため、より製造リードタイムを短縮することが可能となる」(同)としており、2010年度内にはバルク層に適用するための技術開発を終える計画としている。

このほか、光リソグラフィでの量産とのマッチングを図る方法として同社は「TLFD(Target Lithography Friendly Design)」を提案している。これは、各種の電気的特性の互換性を維持するための考え方で、光リソグラフィを用いた際のパターンシミュレーションを基に、それに合わせた形でEBによるパターン形成を行うことで、EBでも光リソでもパターンを同じにしようというもの。「こうした技術もすでにSTARCなどで実証済みであり、スムーズに量産の枠組みに移行することが可能だ」(同)と、問題なくEBから光リソへの移管ができるという。

同社では、こうした取り組みを進めていくことで、多くの半導体製造メーカーでEUVとの並行活用に向けた可能性が開けてくるほか、自社としても試作ビジネスへの適用を通じて、さらなる技術の向上を図っていくとしており、2010年度で12~13億円程度、2015年度ころには20億円規模の売り上げを目指した取り組みを進めていくとしている。