台湾の国立ナノデバイス研究所(National Nano Device Laboratory)と米University of California, Berkeleyの共同研究チームは、セル面積が0.039平方ミクロンと極めて小さなSRAMセルを試作し、その概要を2009年12月7~9日に米国で開催された電子デバイス技術に関する国際会議「IEDM2009」で発表した(講演番号28.7)。これまで国際学会で試作発表されたSRAMセルの中では、最も面積の小さなセルだという。

SRAMセルの試作には、16nmと微細なCMOSプロセスを駆使した。16nm世代のプロセス技術は次々世代のプロセス技術に相当する。現在のところ、半導体技術の研究開発コミュニティでは16nm世代のプロセス技術は固まっておらず、基本技術であるリソグラフィ技術すら、本命が登場していない状態である。

16nm世代のリソグラフィ技術の候補として上がっているのは、光源にエクストリーム紫外線(EUV)を使うEUVリソグラフィと、光源に電子ビーム(EB)を使う電子ビーム・リソグラフィである。発表者のナノデバイス研究所によると、EUVリソグラフィはマスクの製作コストが高騰してしまうことが大きな問題になるという。16nm世代の大規模な半導体チップを試作するためには、マスク代金だけで300万ドルを覚悟しなければならないとする。

これに対して電子ビーム・リソグラフィは、レジストに電子ビームで回路パターンを描くので、マスク代の高騰という問題は生じない。ただし16nm世代では、電子ビーム・リソグラフィも無視できない問題が発生するという。それはシリコン・ウェハに照射された電子ビームが後方散乱によってレジストに飛び込み、露光パターンの乱れを起こすことである。このため、狙った通りの精密なパターンをレジストに描きづらくなる。

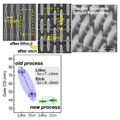

そこでナノデバイス研究所は新しいリソグラフィ技術を考案し、SRAMセルの試作に応用した。シリコン・ウェハの表面にガスを送り込み、電子ビームでガスの化学反応を促すことで微細な絶縁体または導電体のパターンをシリコン・ウェハ表面に形成する方法である。形成した絶縁体または導電体をマスクとして、エッチングによって所望のパターンを作製する。

|

|

|

|

ガスをシリコン・ウェハに供給して電子ビームで化学反応を促し、薄膜(マスク)を堆積する(IEDMの論文集から抜粋) |

電子ビームで形成した薄膜をマスクとしてシリコンの微細なパターンを形成(IEDMの論文集から抜粋) |

このリソグラフィ技術をナノデバイス研究所は、「ナノインジェクション・リソグラフィ(Nano Injection Lithography)」と呼んでいる。マスクとレジストの両方が不要になる、従来とはかなり違うリソグラフィ技術である。

このリソグラフィ技術を駆使して、ゲート長が18nmのMOSトランジスタによる6トランジスタ構成のSRAMセルを試作した。トランジスタのゲート電極は窒化チタン(TiN)、ゲート絶縁膜は厚さ1.6nmのシリコン酸化窒化膜である。ゲート間隔は30nm、ゲートピッチは65nm。リソグラフィに利用した電子ビームの直径は4.6nm、ガスはPtを含む炭化水素ガスである。SRAMセルの寸法は0.30μm×0.13μm。

試作したSRAMセルは、静特性(バタフライ曲線)が測定できる程度のゆっくりとした速度で動いた。電源電圧は0.72V~1.5Vである。電源電圧が0.8Vのときに、160mVの静的雑音余裕(SNM)を確認している。初期の試作結果としては、かなり良好な値だといえる。

IBMは22nmプロセスのSRAMセルを縮小

このほか米IBMが、22nm世代のCMOSプロセスによるSRAMセルを縮小した結果をIEDM2009で発表した(講演番号28.8)。IBMは前回のIEDM2008で、22nmプロセスでセル面積が0.09平方ミクロンと小さなSRAMセルを試作発表していた。

今回のIEDM2009では、セル面積を0.06平方ミクロンとおよそ3分の2に縮小してみせた。前回と同様に、6トランジスタ構成のSRAMセルである。リソグラフィには電子ビーム・リソグラフィと光リソグラフィを組み合わせた。トランジスタ技術はフィンゲートと高誘電率膜/金属ゲート(High-k/Metal gate:HKMG)の併用である。試作したSRAMセルでは、電源電圧が1Vのときに静特性(バタフライ曲線)を測定できている。