東芝は12月9日、チャネル領域の急峻な不純物分布を実現する新技術を開発し、20nmプロセス世代のLSI向けCMOS素子に適用。バルクCMOS技術を同世代に延命できる可能性を示した。同成果については、米国で12月7日より開催されている半導体国際学会(International Electron Devices Meeting:IEDM)において12月9日(現地時間)に発表される予定。

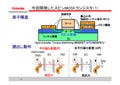

20nmプロセス世代のLSIでは、一般的なバルクCMOS技術ではチャネル部で電子の移動度の低下や、電流を制御するゲート電極のしきい値電圧のバラつきが問題となり、物理的な適用が困難とされていた。この課題に対応するためには、表層を低濃度、奥側を高濃度に大きく不純物濃度を変化させる構造によるチャネル部の急峻な不純物分布の実現が鍵を握るとされているが、これまでの開発成果は、チャネル不純物の拡散しやすいnMOS向けの部分最適化にとどまり、pMOSを含めたCMOS素子全体の最適化を伴う有効な技術ではなかった。

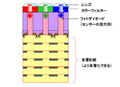

このため、SOI基板や3次元ゲート構造などの新方式の導入によって物理限界を打破することも検討されているが、設備投資の負担や生産効率の低下などが懸念されているのが現状であった。

こうした急峻な不純物分布をつくるためには、「チャネル部に不純物を注入後、表面に新たにSi層を設けるプロセス」および「プロセス中においては避けられない熱工程によって、不純物が表面に拡散しないような構造」「新構造のチャネルが有効に機能するような材料・構造の最適化」といった技術がpMOSにも適用されることが求められていた。

今回東芝は、nMOS、pMOSを効率的に形成する素子構造およびプロセスを新たに開発。従来プロセス比で、15~18%高い性能を実現したという。

|

|

|

20nm世代バルクCMOSに向けた急峻チャネル構造(ゲート電極形成前の不純物拡散層の構造図:手順はB添加Si層を形成し、表面への不純物拡散を防ぐSi:Cによる中間層を形成、そしてエピタキシャル気相成長法によちチャネル表面にSi層を形成するというもの) |

開発された主の素子構造およびプロセスは以下のとおり。

- B添加のSi層を形成。pMOSのチャネル不純物はAs

- 表面への不純物拡散を防ぐSi:C(炭素添加シリコン)の中間層を形成(n/pMOS共通)

- エピタキシャル気相成長法でチャネル表面にSi層を形成(n/pMOS共通)

今回同社が開発した技術のポイントは、効率的なプロセスの実現に向けた材料・構造の最適選択にある。pMOSの不純物を変えSi:C層による拡散防止の効果を検証した結果、Asが最適であることが判明した一方で、pMOSではSi:C層に含まれるCの影響で、絶縁膜などに不要な固定電荷が蓄積することが判明。この問題に対し、Si:C層の直下に新たな中間層としてB添加Si層を設置、CとBの相互作用を活用することで、解決を図った。

これにより、チャネル表面にSi、Si:C、B添加Siの3層を成膜処理により形成、それぞれ低抵抗な通電経路、不純物拡散を防ぐ防御層、炭素による特性劣化を防ぐ緩和層として機能させることで、従来チャネル構造に対する性能向上を実現した。