エルピーダメモリは10月8日、かねてより2009年内の量産開始を計画していた40nmプロセス採用のDDR3 SDRAMの開発を完了したことを発表した。11月にサンプル出荷を開始、2009年内の量産開始を予定している。

同チップはプロセスの微細化により、取れ数が従来の50nmプロセスを採用したDDR3 SDRAM比でウェハあたり44%増加することに成功しているほか、歩留まりも、1.6Gbps品で100%を達成しており、さらなる高速品のサポートも行っていくという。

また、消費電流は50nm品比で約2/3に低減、DDR3標準の1.5V動作のほか、1.2/1.35Vでの動作もサポートすることで、消費電力を従来品比最大45%削減することが可能だ。

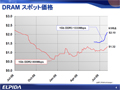

同社では、同プロセスに伴う新規設備投資はほぼ必要なく、既存の50nmプロセスの設備を流用可能としており、コスト競争力を維持できるとしている。加えて、コスト面で競合他社の50nmプロセス品と競合可能な65nm XS(eXtra Shrink)プロセスの開発も進められており、複数の選択肢を用意することで、市況の変化に柔軟に対応し、40nmの設備投資のタイミング、台湾への技術供与の内容などを決定していくとしている。

なお、今後同社では市況の動きを見ながら40nmプロセスのライン構成比を最大50%程度まで引き上げる可能性があるとしており、40nmプロセス品の構成を増やすことで、さらなるコスト削減を実現し、競争力を確保していくとする。