富士通研究所は6月23日(米国時間)、米国ペンシルバニア州立大学にて開催されている国際会議「DRC(Device Research Conference) 2009」において、新構造のGaN HEMTの開発に成功したことを明らかにした。これに併せて、同社は都内で記者説明会を開催、同技術の解説を行った。

今回の成果は、富士通がグループで進めているプロジェクト「Green Policy Innovation」の一環として行ってきた、省エネ化に向けた研究開発の成果の1つ。富士通研究所の取締役 基盤技術研究所長の矢野映氏は、「CO2の排出量が現在の3.3%/年で増え続ければ、2050年までに地球上のCO2量は現在の2倍に到達することが予想され、洞爺湖サミットで排出量を2050年までに現在の半分に収めることが合意された。富士通としても、グループで、デバイスからモジュール、システムボード、サーバ、ファシリティとトータルで技術開発をおこなうことでデータセンタの電力削減を狙っている」と語る。

そのため、今回開発されたGaN HEMTは重要な役割を担うとしており、「従来の電源の変換効率は70%程度であったが、今回開発したデバイスを用いることで変換効率は90%に向上する。これによりサーバ電源の電力損失は1/3に低減されるほか、低抵抗、高耐圧のため、電源装置部品の小型化が可能となり、電源装置のサイズを1/10にすることが可能になる」(同)とする。

同社の試算によると、同デバイスを用いた電源に変える事で国内のデータセンタの消費電力は12%低減(サーバ省電力効果8%、発熱量低減による空調の省エネ効果4%)し、これは年間33万tのCO2削減効果が期待できる値になるという。

また、同デバイスはサーバのみならず、ノートPCに適用すればACアダプタの小型化、本体への内蔵化によりACアダプタをなくすことができるようになるほか、電気自動車や家電、モータなどさまざまな分野への応用が期待できるとする。

これまで同社では無線通信向けGaN HEMTなどを開発してきたが、「電源用とのターゲットとしては、耐記事に通電遮断が可能なオン電圧として+2V以上、+4V以下、およびオン電流として600mA/mm以上を実現する必要があるが、既存のGaN HEMTではオン電圧が0V付近であり、かつオン電圧を正にすると、オン電流(最大ドレイン電流)を高くするのが困難という課題があった」(富士通研究所 基盤技術研究所 主管研究員の吉川俊英氏)とし、新たな構造を開発したという。

具体的には、無線通信用GaN HEMTとして2008年10月に発表した走行電子濃度を増加させる独自の3層キャップ構造の基本はそのままに、「深さ制御をしたゲート掘り込み構造と、原子層レベルの平坦性を実現した酸化膜を採用したゲート絶縁膜」(同)を採り入れたことで実現したという。

深さ制御としては、ドライエッチングで埋め込み前のゲート電極部を掘り込み、n型AlGaNが5nm程度残るまで掘り下げる。「同層を残すことで、GaNの電子走行層へのダメージを与えずに済み、これにより電子走行層の性能を維持できるようになる」(同)とする。一方の平坦な酸化膜は、ALDを用いてAl2O3を積層、これによりゲート電極の平坦性を確保、信頼度の高い通電動作を実現し、オン電流の増加を実現したという。なお、従来の無線通信向けGaN HEMTでは保護膜としてSiNを使用していたが、SiNでは電圧が増えてくると、途中で電子が電極に到達してしまい性能が出せない問題があったという。

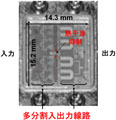

これらの技術により、試作されたトランジスタの性能は、オン電圧が+3V、オン電流密度は829mA/mmと、従来構造比で2倍の値を示し、ターゲットの性能を達成した。この素子の性能は、電源に用いられるSiトランジスタと比べ、オン損失が1/5、スイッチング損失がスイッチングスピード5ns以下で1/100となり、サーバ向け電源装置に適用した場合は、トランジスタ以外のコイルやキャパシタなどの損失を動作周波数を3倍にすることで、Si比で1/2にできることから、電源損失は従来電源と比べ1/3以下にすることが可能になるという。

なお、同社では2011年ころの実用化に向けて信頼性の確認などを進めていくほか、低コスト化技術の開発を進めることで、現在のSiと同等の値段を実現したいとしており、今回の基板はSiCであったが、「SiCウェハの大型化とSiウェハ上での高品質なエピ成長技術の確立の両てんびん」(同)により、より品質とコスト効率の良いほうを見極めたいとした。また、量産の生産担当については、富士通が住友電気工業との合弁会社であるユーディナデバイスに化合物半導体系の製造体制などを移管後、住友電工に譲渡してしまっている経緯から、社内外との連携を模索し、最適な体制を築いていきたいとしている。