NECとNECエレクトロニクスは6月17日、LSI内部のSi結晶欠陥がLSIの待機時電力特性に与える影響を、電子線ホログラフィ法と透過電子顕微鏡法を組み合わせることで、直接観察を実現し、観察することに成功したことを明らかにした。同成果については、6月15日より開催中の半導体技術に関する国際会議「2009 Symposium on VLSI Technology」において発表された。

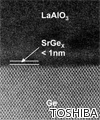

電子線ホログラフィ法は、LSI内部の電位分布を可視化することが可能な技術。一方の透過電子顕微鏡法は、ナノメートルスケールの結晶欠陥の分布や構造を解析できる技術。今回2社は、これらの技術を先端トランジスタのチャネル接合部の評価に適用する技術を開発、組み合わせて用いることにより、ゲート長30nm以下の先端LSIにおける電位分布と微細な結晶欠陥分布の直接観察に成功した。

さらに、同解析技術によって得られた可視化した情報を元に、LSIのリーク電流解析を行い、LSI内部の電位分布と結晶欠陥との位置関係、特に電界強度が大きい領域と結晶分布の位置関係が、LSIのリーク電流に影響を与えることを実証した。

今回開発された技術は、微細プロセスにおいても内部電界と結晶欠陥の直接評価を行うことが可能となり、待機時消費電力低減のための、欠陥・電位分布制御デバイスプロセスの設計に関する課題を実データとして把握することを可能にするもの。

加えて、明らかになった課題に対し、製造プロセスによる改善対策を施したデバイスでは、待機時消費電力の増大の原因となる接合リーク電流の低減効果があることも実証されたという。

2社では、これにより今後、先端LSIの待機時における消費電力低減に向けた接合技術の開発を、効率的に推進できるものとしており、同技術を応用した低消費電力LSIの研究開発を進めていくとしている。