日立製作所とIBMは、トランジスタを構成するゲートの長さが20nmレベルの微細トランジスタにおいて、原子レベルのわずかな構造欠陥によって、トランジスタ動作に必要なゲート電圧(しきい値電圧)が、平均値の10倍以上の幅でバラケースが、1,000個に1個(=0.1%)の割合で存在することを実験的に確認したことを明らかにした。同成果は、2009年6月15日から京都で開催されている半導体技術に関する国際会議「2009 Symposium on VLSI Technology」で発表される。

同バラつきは、ランダムテレグラフノイズ(Random Telegraph Noise:RTN)と呼ばれる現象により生じるものだが、今回の実験結果は、今後、何の対策も講じなかった場合には、最先端プロセスにおける複数のトランジスタを組み合わせてメモリセルを構成するSRAMでは、RTNの影響により、LSIそのものが動作しなくなることを示唆しており、回路線幅が22nmの次々世代半導体デバイスの開発において、RTNのメカニズムの解析や評価の重要性を示す成果といえる。

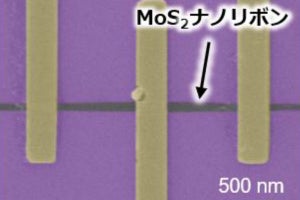

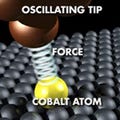

今回、両社の研究チームが注目したRTNは、トランジスタを構成するゲート絶縁膜に存在する原子レベルの構造欠陥に電子が捕獲または放出されるのに連動して、トランジスタを動作させるのに必要なしきい値電圧が時間的に上下に変動するというもの。以前より、トランジスタの不安定動作要因として知られていたが、RTNによるしきい値電圧の変動量は、これまでのLSIでは、LSIの動作電圧マージンで対応できたことから、顕著な課題として取り上げられてはこなかった。しかし、トランジスタの微細化が進み、ゲート長が20nmレベルになると、RTNの要因となる構造欠陥の存在確率は減少するものの、RTNによる変動量はゲート面積に"反比例"することから増大し、LSIの動作電圧マージンで対応できなくなることが予測される。

そのため両社では、IBMの先端プロセス技術と日立の解析技術を融合させ、20nmレベルの微細トランジスタを試作。約1万5,000個の実デバイスを用いたRTNの評価実験を実施し、RTNによるしきい値電圧のバラつきは、正規分布から予想されるよりも、分布の裾で大きな振幅を持つことを突き止めた。具体的には、しきい値電圧のバラつきの平均値が数mVであるのに対し、70mVの幅で変動を示すトランジスタが、1,000個に1個(=0.1%)の割合で観察されたという。また、この確率は、将来のSRAM設計において、何も対策を講じなかった場合においては、LSIそのものの動作が困難になることを示唆するものとなることを明らかにした。

なお、両社では、今回の評価結果について、回路線幅が22nmとなる次々世代の半導体デバイスの開発において、RTNのメカニズムの解析や評価の重要性を示す成果としている。