富士通、富士通研究所およびFujitsu Laboratories of Americaら、65nmのCMOSプロセスを用いて、40Gbpsの基幹系光伝送システム向け送信ICを開発したことを明らかにした。従来、40Gbpsを実現する回路は、化合物半導体を用いて製造されていた。今回のCMOSプロセスでの回路技術は、1チップ化のほか、伝送装置の低消費電力化、小型化、低コスト化を実現する技術として期待される。

CMOSプロセスにより40Gbpsを実現するためには、データを伝送する回路の動作速度を向上させるだけでなく、回路動作のタイミングを決定するために回路に供給されるクロック信号に関して20GHzで低ノイズかつ十分な振幅を確保することが重要であった。ただし、配線や素子に付随する寄生容量による損失により、クロック信号の振幅は劣化する問題があり、寄生容量の影響をどれだけ抑えられるかが課題となっていた。

また、CMOSプロセスでは、微細化に伴い、トランジスタの耐圧が低下するため、電源電圧が1.2V以下に低下。このため、供給電源に変動が生じることで、回路に十分な電源電圧が供給されず、不安定動作を引き起こす原因となっていた。

今回、送信IC内のクロック伝送回路に低消費電力で低ノイズのクロック伝送を可能とする新しいインダクタ補償技術を開発した。これは、送信IC内のクロック信号が単一周波数であることに着目し、クロック信号の周波数に近い領域のみインダクタで寄生容量を補償する新しい高速化技術を適用することで、従来に比べて少ない回路段数でノイズの少ない高速クロック信号伝送を可能としたもの。

また、回路動作を制御するクロック信号と回路を通過するデータ信号のタイミングを常に監視し、相互の信号の関係が最適になるように、動的に調整する新しい回路技術を出力回路に適用した。同回路技術は、監視、調整する機構を、データ信号の伝達経路から分離した構成を採用したことで、監視、調整回路の追加によるデータ信号の波形の劣化を引き起こすことなく、自動的に相互の信号のタイミングを最適化し、高速で安定した波形の送信が可能となっている。

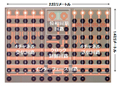

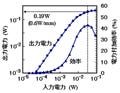

これらの技術を用いて65nm CMOSプロセスで信号生成回路、低速側インタフェース回路、制御回路などを集積、1チップ化を行った。このICの出力波形は、安定しており、実用上もとめられる電源電圧の変動範囲で、確実に"0"と"1"が判定可能な40Gbpsの出力信号が生成できることが確認されている。この結果、新たに開発した回路技術が、電源電圧の変動だけでなく、送信ICの使用温度の変化による影響に対しても有効であることが確認されることとなった。

また、1チップ化、新規クロック伝送回路の採用などにより、消費電力を従来比1/3以下となる2W以下に抑えることに成功。低発熱のため、光伝送装置内への光送受信モジュールの高密度な実装が可能となる。そのため、同ICを用いる場合、従来の40Gbpsの伝送装置と比較して、約1/2の小型化が可能となり、低コスト化も見込めるという。

同ICは、低速側インタフェースとして、「SFI 5.2」を採用している。また、長距離伝送のための信号変調方式に対応する20Gbpsの信号2本を出力する機能が付加されている。

3社では、今後、出力波形のさらなる改善を行っていくほか、CMOSプロセスによる受信ICの開発を促進し、光伝送装置の小型化を進めていくとしている。また、今回の開発成果は、基幹光伝送システムだけではなく、将来的にはLANや企業ネットワークの高速化の実現に向けた、40Gbpsイーサネットシリアル光伝送装置などへの適用も進めていくという。