IBMとAMD、Freescale Semiconductorの共同研究チームは、22nmと微細な半導体プロセス技術を開発し、SRAMセルを試作した結果をIEDM 2008で発表した(講演番号27.1)。

講演では始めに、スケーリング(微細化)の基本的な方針を述べた。過去の45nm世代と32nm世代では、トランジスタのゲート長が38nmのままであり、縮小されていなかった。22nm世代ではゲート長を一気に25nm以下に短縮することを目指した。このために、隣接するトランジスタの間にあるスペーサの幅を20nm以下に縮めた。また、コンタクトホールの直径をホールの底で26nm以下に縮小することにした。

基本的な設計ルールはゲート長25nm、ゲートピッチ90nm、アクティブ層の幅52nm、アクティブ層のスペース50nm、コンタクト26nm、コンタクトピッチ90nm、金属配線幅40nm、金属配線スペース50nmである。トランジスタには高誘電率膜/金属ゲート(High-k/Metal gate)技術を導入した。アクティブ層は45nm厚のSOI層である。

試作したトランジスタの断面を電子顕微鏡で観察した像(IEDM実行委員会のプレスキットから抜粋) |

これらの設計ルールに基づく微細加工を実現するため、リソグラフィにはArF液浸露光とダブルパターニング(ダブル露光とダブルエッチング)を組み合わせた。トランジスタはGate-firstの順番で製造する(金属ゲートを形成後に、高誘電率膜をパターニングする)。

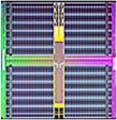

試作したSRAMセルは6トランジスタで、セル面積は0.1平方ミクロンと小さい。静的雑音余裕(SNM)は電源電圧が0.9Vのときに220mVである。また、セル面積が0.09平方ミクロンとさらに小さなSRAMセルも試作してみせた。SNMは電源電圧が0.9Vのときに160mVを得ている。なおトランジスタの性能(飽和ドレイン電流など)は発表しなかった。

試作したSRAMセルの電子顕微鏡観察像。セル面積は0.1平方ミクロン(IEDM実行委員会のプレスキットから抜粋) |