6月のCOMPUTEXで予告されたZen 5ベースのRyzen 9000シリーズやRyzen AI 300シリーズであるが、こちらの記事の最後で触れた様にTech Dayが開催され(ちなみに筆者は不参加)、そこである程度細かい情報が出て来た(といっても、例えばROBやIn-Flight Bufferのサイズといった、本当に細かい話はあまり出ていないのだが)。そこで現状公開された話をまとめてご紹介したい。今回はまずZen 5のコアそのものと、Ryzen 9000シリーズについてである。

Zen 5コア

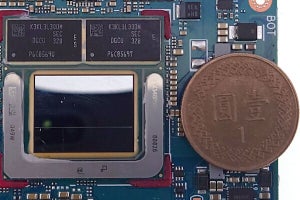

まずZen 5コアの設計目標がこちら(Photo01)。中々増えなかったFront Endの同時デコード命令数も増やされ、これに合わせてBack Endも強化された。またData CacheのBandwidthが倍増というのは、恐らく後述するFP/Vectorの対応と思われる。

そのFront End(Photo02)だが、まずDecodeは4-wide×2に強化され、これに伴いOp Cacheも6K Instruction×2と猛烈に強化されている。Zen 4のアーキテクチャと比較すると、フロントエンドのデコード能力はほぼ倍増した格好だ。Op Cacheからの帯域もトータル12命令/Cycleで、Zen 4の9命令/Cycleからだいぶ強化された。

この4-wide×2というのはThread毎にそれぞれ4-wideという形と考えられる。尤も、ではBIOS Setupの中でSMTを無効化すれば、これがIntelのTremontなんかと同じように8-wideとして動作するのかどうか? は確認できていない。ただ構造的に見れば、そういう動作を行う事はそう難しくない様に思える(これはOp Cacheに関しても同じである)。

Dispatchは8命令/Cycleであり、これはZen 4の6命令/Cycleから若干の増加だが、Decodeの方が常にフルに8命令/Cycleでデコードできる訳でもないから、妥当なところかと思う。分岐予測は2-taken/2-aheadとなっているが、要するにZen 4世代のものの2倍の処理性能ということになる。これもまぁThread別に用意された、と考えればわかりやすい。

ちなみにこのFront End、IntelのLion Coveと全く同一のスペックになったのは偶然だとは思うが、逆に言えばx86を強化してゆくと必然的に同じ様な構成になる、ということだろうか?

一方のBack End側(Photo03)であるが、まずALUは8-wideとなり、ALU×6、MUL×3、Branch×3とAGU×4という、これもどこかで見た様な猛烈な構成になっている。Physical Registerも240entryと猛烈に大きくなっている。

-

Photo03: IntelはLoad/Saveで別々のAGUを割り当てるが、AMDは同じAGUになっている。ただこれは表現の違いであり、Intel風に言えばこのZen 5にはLD AGUとSTR AGUがそれぞれ4つづつある事になる。

一方FPU/Vector(Photo04)であるが、こちらはLion Coveよりもさらに強力な構成である。Lion CoveはClient向けにAVX512をサポートしない関係でか、256bitのSIMD演算を同時に4つ可能(ただし組み合わせても512bitにはならない)のだが、Zen 5では512bit演算×2と、それに加えてFPU用のLoad/Storeユニット(多分であるが、右端の2つの"StD/IntD"ユニットはLoad/Storeユニットと思われる)を搭載している。実はこれに絡む話で、Chips and CheeseのGeorge Cozma氏がAMDのMike Clark氏にインタビューしている動画(とそのTranscript)が公開されているのだが、この中で

George Cozma: Yep, and you can do two stores per cycle of any size.

Mike Clark: You can use two stores per cycle of any size.

という下りが最後の方に出てくる。ここで言う"any size"は128/256/512bit幅であることがこの直前で議論されており、つまり512bitのStoreを1cycleあたり2つ(合計128Byte)実行できることになる。これはALUの方には不必要な規模のStore能力であり、AVX512の利用時にのみ使われることになる。多分その辺りもあって、ALUとFPUでLoad/Storeユニットを別々に搭載したものと考えられる。

当然ここまで性能を強化すると、Cacheの側も強化する必要がある。ということで帯域を倍増した(Photo05)という話である。Zen 4では256bitのSIMD演算を同時に2つ(つまり64Bytes/cycle)処理できたから、倍増だと(先ほどのMike Clark氏の発言の様に)128Bytes/cycleの書き込みが可能になったものと考えられる。この帯域はなかなか驚異的であり、Consumer向けのCPUでこれが消費電力を大幅に増やすことなく可能になったというのは、なかなか大した偉業と思われる。

ちなみにL1のLoad Latencyが4cycleというのは。以前RMMAを行った際の結果もZen 3/Zen 4共にL1は4cycleだった事を考えると、「Latencyを削減した」のではなく「機構が複雑化したにも関わらずLatencyを増やさずに抑えた」というのが正しい意味合いかと思われる。

これだけFront End/Back End/Cache周りを強化すれば、それはIPCも向上しようというものである。Photo06はGameを含む様々なベンチマークでの性能改善率で、平均16%の向上が実現したとしている。GeekBench 5.4.6での結果ではZen 4から32~35%の性能向上が実現したそうだ。

-

Photo06: これはRyzen 9 9950XとRyzen 7 7700Xを比較しての数字との事。ただし動作周波数を4GHzに固定しての結果だそうで、まぁ確かに概ねIPCの比としても差し支えはないだろう。

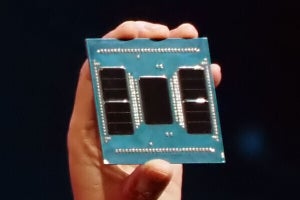

このZen 5、まず当初はRyzen 9000シリーズに4nmプロセスで投入されることになるが、3nmまで対応を想定しているそうで、Consumer向けは来年の製品に持ち越しということになりそうだ(Photo08)。ではServer向けのEPYCは? ということだが、こちらはこちらでまたとんでもないスライドが出て来た(Photo09)。COMPUTEXの基調講演で出て来たスライドと比較すると「これは何だ?」という話になる訳だが、こちらの記事の中でDavid McAfee氏がZen 5cベースのEPYCの存在を匂わせる発言をしたことをお伝えしている。ではZen 5ベースのEPYCは? というのが恐らくこのPhoto09である。つまり

- COMPUTEXでのスライド:Zen 5cベースで、1つのCCDにCCXが2つ(つまり16core)搭載され、最大12CCD、192core/384thread。これはBergamoの後継製品と目される。

- 今回のスライド:Zen 5ベースで、1CCDにCCXが1つ(つまり8core)搭載され、最大16CCD、128core/256thread。これはGenoaの後継製品と目される。

という2種類の製品SKUがあるという話だ。このGenoaの後継製品の方は、Ryzen 9000シリーズと同じCCDをそのまま流用する形だろう。

また今回のスライドで、やっぱりIODは作り直しになった事がほぼ確定した。理由は、Genoa世代までのIODは最大で12本のInfinity FabricのLinkしか持たないためで、COMPUTEXで公開されたバージョンはともかく、今回公開されたバージョンでは対応が出来ないためだ。元々Turin世代の場合、コア数が増えてもメモリバスそのものは(既存のGenoa Platformを利用するから)12chのままで、どう考えてもコアの数(というか、コアが要求するメモリ帯域)と提供できるメモリ帯域がマッチしておらず、MRDIMMの利用は必須と思われるのだが、GenoaのIODでMRDIMMが使えるという話は聞いていない(MRDIMMの開発開始時期を考えると、GenoaのIODでサポートできるとは考えられない)から、MRDIMMに対応した新IODが出てくる可能性は高いと思っていたのだが、今回これが新しいものになる事がハッキリ確定した格好だ。

残念ながらEPYCに関しての情報はこの程度に留まっているが、なかなか楽しい事になりそうである。とりあえずGranite Rapidsを迎え撃つ準備は十分に出来ている様だ。

Ryzen 9000シリーズ

そんなZen 5コアを搭載するRyzen 9000シリーズであるが、当初のラインナップはこの4製品(Photo10)。出荷開始は7月31日とされる。現状はまだあまり細かい話は無いが、Ryzen 9 9900X vs Core i9-14900K(Photo11)、Ryzen 7 9700 vs Core i7-14700K(Photo12)、Ryzen 5 9600 vs Core i5-14600K(Photo13)の3つを示し、いずれも大きなアドバンテージがあるとした。また変わったところでは、Ryzen 9 9700X vs Ryzen 7 5800X3Dでのゲームでのフレームレート比較も行い、3D V-Cacheのハンデがあっても平均12%の性能向上が実現しているとした。

また熱抵抗を15%削減したことで、同じTDPなら温度を最大7℃下げられるとしている(Photo15)。まぁこれはヒートシンクの種類とかにもよるのだろうが。またRyzen 7000シリーズと比べて、基本消費電力を落としながら、性能はむしろ改善しているとする(Photo16)。

-

Photo16: これは消費電力の多さが故障に繋がると噂されているRaptor Lakeへの当てつけの面もありそうな話ではあるが、Ryzen 7が全部TDP 65Wになったのは個人的には大歓迎したいところだ。

細かいところでは、OC Memoryでは最大DDR5-8000まで、定格動作ではDDR5-5600までサポートしたとする(Photo17)。このスライドの最後に出て来たCurve Shaperの説明がこちら(Photo18)。要するに、よりきめ細かくOC時の動作を制御することで、よりギリギリまで動作周波数を引き上げられる様にした、という事である。このCurve Shaperと組み合わせる形で利用するPBOは健在であり(Photo19)、6~15%の性能改善が可能としている。

-

Photo18: 従来のCurve Optimizerでは、単純にHiかLowしかなかったのが、Curve Shaperではある動作周波数の先から、状況に応じて細かくOCできる範囲を制御できるという事だ。OCし過ぎでCPUを破損しないギリギリまで引き上げられる、という訳だが個人的にはもうOC動作止めない? という気もしなくはない。

次にチップセットの話。800シリーズはこの4製品が提供予定とされる(Photo20)。USB 4が必須なのはX870/X870Eのみで、B850/B840はUSB 3.2のサポートのみ。構成そのものは以前こちらで触れた格好で、今度はX870が基本となり、これを2つ繋げたのがX870E、X870の機能削減版がB850になる感じだ。B840はA620あたりのRefreshという事だろうか? 拡張性が必要ない用途(例えばNUCの様な省スペースPC)向けという感じに見える。

ちなみにIntelは依然として、CPUから出るx4レーンをPCIe 4.0に据え置いている。それもあってか、こんなスライド(Photo21)も示されていたが、ちょっと趣味が悪い様に思う。とはいえ、今年後半には消費電力が低い(=爆熱ではない)PCIe 5.0 SSDがコンシューマ向けにも出てくる模様なので、確かに一理あると言えばあるのだが。

-

Photo21: Z790は、x16レーンにはPCIe 5.0が出ているが、x4レーンはPCIe 4.0である。なのでPCIe 5.0対応SSDを使った場合、GPUをあきらめてx16レーンに装着する(GPUの接続が犠牲になる)か、PCIe 4.0レーンに装着する(ので帯域が半分になる)事を揶揄するスライドである。

ということで、現状Ryzen 9000シリーズの情報を簡単にまとめてみた。7月末には出荷ということで、その頃には詳細な評価結果もお届けできるかもしれない。もう少々の辛抱である。