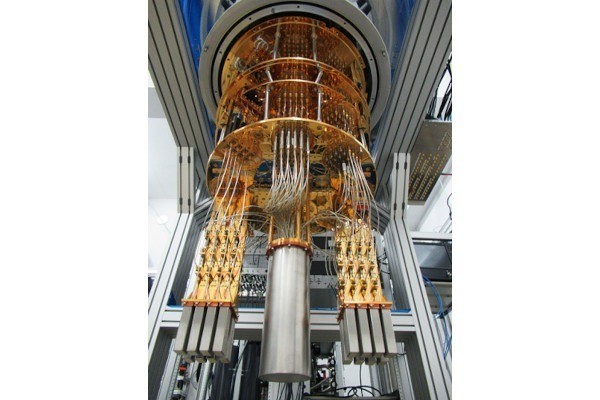

よく見る量子コンピューターの写真は冷凍機(の一部)

理化学研究所は2023年10月5日、「理研RQC-富士通連携センター」で開発した64量子ビット超伝導量子コンピューター二号機を報道陣に公開しました。また、10月11日富士通も研究戦略説明会を行い、量子コンピューターのモックアップ展示を行いました。

-

2023年10月5日に理化学研究所で公開された超伝導量子コンピューター国産二号機(中央)と理研の中村泰信・量子コンピュータ研究センター長(右)と富士通の佐藤信太郎・量子研究所長(左)

-

超伝導量子コンピューターの中はこんな感じ。上から段階的に冷やしていき、御本尊である量子チップを20mKの極低温まで冷やします。遮熱カバーが入っているため、稼働状態では内部構造を見ることはできません

理化学研究所(以下理研と略記)で稼働している超伝導コンピューターは、これで二基目。3月に公開された初号機(愛称:叡)は、理研と学術機関が共同研究で学術利用するのに対し、今回発表された二号機は40量子ビットのシミュレーターも含めたプラットフォームとして、産業界との共同研究を行い量子コンピューターの社会実装のために使用予定。目的が大きく異なっています。

仕様としては、理研の超伝導量子コンピューターは初号機も二号機も64量子ビット。理論的には最大で2の64乗個の状態の重ね合わせ計算が可能です。

ちなみに、筆者が東京にあるクラウドデータセンターに英国生まれの量子コンピューターが設置されると言われ、取材に行ったのが今年の3月のこと(関連記事)。ついに量子コンピューターの実物を見ることができると期待したのですが、見せられたのは先のリンク先のもの(写真撮影不可で、この記事に掲載されているのは公式提供画像)……いや、これ量子コンピューターというより、冷凍機の先っちょじゃん!

量子コンピューターのご本尊を拝めなかったのにももちろん理由があり、現在の超伝導量子コンピューターは量子力学的な現象を扱うためには、熱ゆらぎを可能な限り取り除く必要があります。つまり、極低温に冷やさなければいけないというわけ。

これ以上冷やすことができないと言われる絶対零度(0K)が-273.15℃。だいたい20mKが現在の超伝導量子コンピューター素子の動作温度なので、つまり-272.95℃まで冷やす必要があります。先の写真はその冷凍機で、上から段階的に冷えていき、一番下のところで20mKになるという仕組みです。

本来ならば冷凍機の一番下に量子チップが収められているはずですが、写真を見ると組み込まれていませんし、量子チップのビット状態を制御したり、読み出しに使う同軸ケーブルもありません。見学時点では、写真のラックの左右にあるはずの冷凍制御装置も量子状態を制御する装置もないという組立途中の状態でした。

本来の稼働状態にある超伝導量子コンピューターは、外来ノイズを減らすために量子チップの周りをシールドで遮蔽したうえで、遮熱のカバーをかける仕組みになっており、「白いペール缶」のような画像を超伝導量子コンピューターとして出しているのを見たことがある方もいると思います。でもこれではあまり見栄えがしないという問題が。

今回の記事で扱っている理研の説明会でお目見えした一番上の写真も、やはりビジュアル的にはいまひとつという趣があります。

-

せめてという事で内部構造のプロジェクションマッピングもされていましたが、イマイチでした。これの実物を見たい

-

一方、初号機から製造を改良した量子チップの見本の顕微鏡画像も用意され、現時点での不良状況も説明されていたりと、情報公開度はかなり高かったように思います

オッと思ったのは、11日の富士通 研究戦略説明会の後には、展示会場で「冷却装置のモックアップと超伝導量子チップの展示」があったところ。隣にPRIMEHPC FX1000のモックアップもおいてあり、量子シミュレーターに使う計算機と超伝導量子コンピューターの両方を見せていたのは見ごたえがありました。

この量子シミュレーターに使う「PRIMEHPC FX1000」は、FX700と同じプロセッサ「A64FX」を富岳同様に水冷仕様で内蔵し、最大384ノードを収容したサーバー。価格は最小構成の48ノードでなんと1.2億円という高価な計算機です。

-

富士通 研究戦略説明会の後のデモ会場に階段を下りる途中に置いてあったのが、超伝導量子コンピューターの中身のモックアップ。これが見たかったんです。説明員によると本物は同軸ケーブルがもう少し細いとの事

-

その横富岳で使われているものの商用機「PRIMEHPC FX1000」。この筐体で最大384ノードが収められるため、40量子ビットのシミュレートにはこれが3台必要という事になります

-

モックアップの下は鏡になっており、量子チップが見やすくなっているのもうれしいところ

-

量子チップ周りの拡大。後ろに見えるのは電磁場の影響を抑えるためのカバーで、本来なら覆われているのですが、見やすく切り裂かれた状態になっています。量子チップは裏面からプローブで接触しており、他の超伝導量子コンピューターよりもすっきりしています

-

量子チップからケーブルを引き回している関係で、アンプやフィルタが中に収められています

-

量子チップ。黒い大きめの丸い部分が量子ビットを構成するジョセフソン素子で、4つが1ブロックを構成しています

-

信号はチップの裏面からやり取りするため、細い穴を開けて導体を埋め込んでいるとの事

今後のスケールアップにも耐える? 理研の超伝導量子チップ

理研の超伝導量子チップの特徴は、4つの量子状態を1つの端子で読み出すことができる仕組みと、配線を裏面に回している点です。前者は共振周波数を微妙に変えて4つの量子ビット状態を読み出せるところがポイントで、後者は今後量子ビット数が増えても配線方法を大きく変化させなくてもよいのがメリットになります。このためにチップに穴を開け、裏面まで導通を取るようにしています。

-

理研の超伝導量子コンピュータの概要。量子ビットの制御と読み出しの配線をシリコンチップの裏面から行うのが特徴。また、読み出し配線も4ビットを1つの配線で行うのでケーブルの総数が少なくなります

-

理研と富士通の量子コンピューター開発の取り組み。1,000量子ビットが当面の目標となっています

下からプローブを当てていることからチップの厚みを削るのは難しいかなと思ったところ、「チップは削っていない」とのこと。穴を開けるよりも導体(アルミ)を詰める方が難しいそうです。この方法ならチップ内の量子ビット数を増やしても基本構造が変わらず、(冷凍機の大型化が可能ならば)チップをタイル型に並べて配置し、スケールアップが容易というメリットがあります。

なお、さらなる量子ビット数を達成するためには配線数を減らす工夫も必要。現在の64量子ビットの制御のためには入力配線96本/出力配線16本の計112本の配線が必要ですが、量子ビット数が増えればそれだけ配線も膨大になります。

なぜ現行量子コンピューターでは力不足で、暗号技術は強固なままなのか

そもそも、量子コンピューターとは量子力学の原理をコンピューターに応用したもので、今までのコンピューターが二進数をベースとして1つ1つ処理を進めていたのに対し、量子コンピューターは量子の重ね合わせ状態を利用して一括処理ができるところにあります。

たとえば、現在暗号化によく使われている「RSA暗号」や「楕円曲線暗号」は従来のコンピューターで力任せに解くには時間がかかり過ぎます。「量子コンピューターによって暗号が解かれてしまう」と言われているのは、「十分な強度の暗号を解く能力のある量子コンピューターは、まだ存在していないハズ」というのが現時点の技術的立ち位置。

つまり、今使われている暗号は有意時間で解けないほど十分な強度を備えているため、現在では安全と言われているわけです。

具体的な例で説明すると、例えばマイナンバーカードには現在2,048 bitのRSA秘密鍵が入っています。第三者がこれを無理やり解読するためには、現在最高性能のスーパーコンピューターでも1億年以上かかると言われています(性能が1万倍になっても1万年)。

対して、1万量子ビットの量子コンピューターを使えば約104日へと短縮できるという試算を富士通が発表しています。

「1億年から104日」への短縮は圧倒的な差。とは言え、少なくとも1万量子ビットの量子コンピューターが現在稼働しているという情報はありません。さらに、現在の量子コンピューターはNISQ(Noisy Intermediate-Scale Quantum Computer)、つまり誤り耐性がなく、104日間も量子状態を安定的に保持できないため、最終的な出力が正確ではないという問題もあります。

じゃあ将来は? と先のことに目を向けると、マイナンバーに限らず大半の電子署名には有効期限が設定されており、先に挙げたマイナンバーの場合は5年。5年後の更新時に今後5年以上テクノロジーの進歩があっても、安全な暗号方式に変更されていれば利用者目線では問題ありません。

-

マイナンバーカードには署名用の2048bit RSA暗号鍵が含まれていますが、現時点ではこれがすぐに破られるという事はありません。また暗号鍵には有効期限があり、有効期限に達した時点でさらに強力な暗号鍵を使っているでしょう

また、現時点では超伝導量子コンピューターに使われている素子もバラツキがあります。理研で作成したものは、極低温で動作するジョセフソン素子を使用したもので、20mm角のチップに64の素子を並べていますが、初号機の際には製造のばらつきが3.4%あり、64の量子ビットのうち11は利用できず53量子ビットで研究をスタートさせています。とはいえこれも、量子ビットの維持時間も数十マイクロ秒に留まっているようで、大きな量子計算を行うには短いように思えます。

二号機の製造にあたっては描画寸法を変えることでバラツキを1%程度に抑えましたが、それでも64の量子ビットすべてが完璧に動作しているわけではないため、今後も量子ビットチップ製造の改良が必要でしょう。資料を比較すると、量子ビットの維持時間は50%ほど伸びているので、改善されているのがわかります。

-

初号機から量子チップの製法に改良が加わっており、チップのバラツキを軽減させています

-

しかし、現時点での二号機は3つの不良ビットと量子状態保持が悪いビットが6個存在します。おそらく今後製法に改良を加えて交換されるのでしょう

なお、現時点でも誤り耐性のある量子コンピューターとして、量子シミュレーターがあります。富岳と同じCPU「A64FX」を内蔵する計算機「PRIMEHPC FX700」を8台、64ノードで動作させることで、世界最速を誇るという36量子ビットの量子シミュレーターが存在します。

2023年7月には規模を大きくして1,024ノードを組み合わせ、最大40量子ビットのシミュレーションも可能となりましたが、これ以上の規模拡大は難しいとのこと。また、シミュレーターなので演算に長い時間がかかり、本来量子コンピューターに期待されるような短時間で完了することができません。

-

20mKと極低温にしても、熱の影響を完全に排する事はできず、また外来ノイズが悪影響を及ぼすので結果にエラーが出ます。多くの量子ビットを使いつつエラー耐性のある量子コンピューターが登場するのは10年以上先、と予測されています

-

エラーの無い量子コンピューターとして量子シミュレーターがあり、富士通は富岳のテクノロジーを活用した商用機PRIMEHPC FX700を8台、64ノード使用した環境で36量子ビット、1024ノードにする事で40量子ビットまで拡張しています

そこで今回の理研と富士通の取り組みとしてポイントになるのは、ハイブリッド量子コンピューティングプラットフォームを作り、量子コンピューターと量子シミュレーターをシームレスに運用するというところにあります。

量子コンピューターはエラーの問題があるので、大ステップの演算を行うとエラーが多くて使えません。一方、量子シミュレーターはエラーがないため大ステップ演算が行えますが、実行時間が長くなります。

なので、2つのアプローチが紹介されています。1つは量子コンピューターと量子シミュレーターに同じ問題を入れることでエラー緩和が可能になるか活用するというもの。もう1つはお互いのメリットを生かして問題を分割し、量子コンピューターと量子シミュレーターを組み合わせるというものです。

事例として、水素原子が12個つながっている分子に対し、分割した演算を量子コンピューターで行い、ノイズを補正したのち、得られた結果を量子シミュレーターで合算。従来の古典近似計算よりも高い精度での演算が行えたと紹介していました。

-

現時点の解として量子コンピューターと量子シミュレーターを組み合わせたハイブリッドプラットフォームを構築しました

-

量子アルゴリズム精度評価と量子コンピューターと量子シミュレーターを組み合わせたアルゴリズムというアプローチが考えられています

-

現実の量子コンピューターは長い演算を行うとノイズの影響が顕著となります

-

そこで部分的な演算を量子コンピューターでおこない、その結合演算を量子シミュレーターで行う試みを行いました

なお、量子コンピューターが実用になる将来では、複数の量子ビットによって誤り訂正を行うFTQC(Fault Tolerant Quantum Computer)となるといわれていますが、ここにたどり着くためには100万量子ビットの素子が必要になると言われています。

富士通のロードマップを見ると、2026年以降に1,000物理量子ビットの量子コンピューターを作る計画となっており、量子コンピューターで実用的なアプリケーションを作るのはまだかなり先という感じです。

現時点では素子のバラツキや外来ノイズに非常に弱く、量子ビット数もさまざまな実用アプリケーションとして使うには程遠い。これが現在の量子コンピューターの現実で、まだまだ研究レベルと言えるでしょう。