高信頼性を誇る日本の技術は業界の基準になりうる

需要が一気に高まる3Dパッケージング技術について、日本国内の半導体メーカー各社は、それぞれの製品開発の中でさまざまな技術開発を進めてきており、その技術は世界でも存在感を発揮するという。

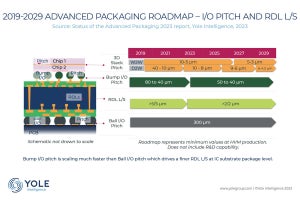

チップレット化において重要な技術としては、複数の半導体と基板をつなぐ際に、中継部材のインターポーザ―を使わずにチップ同士を接続する「ブリッジ構造」や「再配線層(RDL)」などが挙げられる。電気特性の改善につながるこうした接続技術は、各メーカーが独自に開発・実用化を進めているため、激しい競争によって性能向上が進んでいるとする。

ハイブリッド接合やサブストレートの微細化など、さまざまな技術を組み合わせるチップレット化に向けては、技術と材料の両面で進歩を遂げている日本の優位性があると菅沼教授は語る。実際に、先般開催されたG7に際して、岸田文雄首相と世界の大手半導体企業トップとの間で意見交換が行われた際には、Intelをはじめとする各企業が、パッケージングなどの後工程に関する拠点の日本への設置を検討する姿勢を見せるなど、国際的な注目を集めている。

また、日本の半導体技術が注目される背景には、信頼性に対する要求の高まりもあるとのことだ。近年の半導体需要拡大は、AIと並んで自動運転の普及が牽引しており、社会インフラにおける需要も高まっている。人命や社会活動に関わるこれらの領域で使用される半導体に対しては、性能と同時に信頼性の高さも必ず求められる。性能向上を目指す上で切り離せない熱効率の改善なども信頼性に大きく影響するため、これらを向上させる3Dパッケージング技術の開発が必要とされる。菅沼名誉教授は、「高信頼性と高機能の両立は、もとより日本が強みとしている部分」と語り、日本の製品が世界標準になる可能性も十分に考えられるとしている。

チップレット技術の普及や低コスト化に向けた国際的なオープン規格として「UCIe」が立ち上がるなど、チップレット技術においては国際標準化が進んでいる。「世界のスタンダードを決めていく中で、日本がその流れに寄与していくことが望ましい」と菅沼名誉教授が語るように、発展途上のチップレット化において日本の技術がどれほどの存在感を放つことができるかが、今後の半導体開発競争に大きく影響していくと考えられる。

産学連携による人材の育成・確保が重要

学術機関に所属する菅沼名誉教授は、講演の最後に、台湾における半導体産業を支える高等教育体制を例示しながら、半導体産業の人材体制に言及した。

半導体産業が盛んな台湾では、TSMCやASEなどの半導体企業の拠点と、トップ4大学が、非常に近い場所に位置しているという。またこれらの大学では、法整備により2022年から半導体学科が設置されているとのことで、国家をあげて半導体産業に注力している姿勢が見られる。

台湾を視察した際には「学生たちの目がキラキラしていて、非常にうらやましい環境だった」といい、産業と学術機関が連携しやすい体制づくりの重要性を強調したうえで、「人材が育つ場所でこそ企業が育つ。こういった環境づくりを日本でも行っていきたい」と今後の展望を語った。