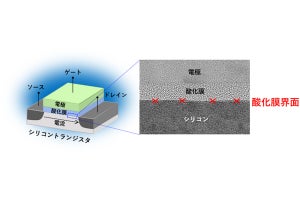

研究チームはまず、対象となるLixWO3ベースの酸化還元トランジスタを作製。厚さ0.15mmのLIGCG基板上に、ドレイン電極とソース電極として50nmの白金薄膜を、その上に100nmのWO3薄膜を製膜した。ゲート電極としては、200nmのLiCoO2がWO3層とは異なる側に製膜され、その上に集電体として50nmの白金薄膜を作製した。そしてリザバー演算を開始する前に、ゲート電極とソース電極間に2.5Vの定電圧を1時間印加することにより、LiイオンがWO3チャネルに挿入されたLixWO3相が形成したとする。

次に、作製した酸化還元トランジスタを物理リザバーとして使用し、時系列入力に対する二次非線形動力学方程式を解くことで、演算処理の性能評価を実施した。その結果、ドレイン電流のみを使用する条件(単一リザバー)では予測誤差8.15×10-4、ドレイン電流とゲート電流を組み合わせた条件(二重リザバー)では予測誤差5.39×10-4という、極めて小さな値が得られることが判明。これらの値は、スピントルク発振素子やメモリスタなど、これまでに報告された、異なる種類の物理リザバーよりも高い精度で演算処理できることを示すとしている。

続いて、時系列予測の性能を詳しく評価するために、物理リザバーコンピューティングの代表的なベンチマークである「非線形自己回帰移動平均タスク」を実行したとのこと。二次非線形動力学方程式と同様に、二重リザバー条件では、「規格化平均二乗誤差」が0.163となり、より優れた性能を示すことが確かめられたという。

さらに、ゲート電流の利用による性能向上のメカニズムを調べるために、短期記憶タスクが実行された。その結果、単一リザバー条件では記憶容量は2.35だったのに対し、二重リザバー条件では、記憶容量が3.57に増加することが明らかになった。研究チームは以上の結果から、ドレイン電流とゲート電流の非線形応答により二重リザバー状態が実現し、高次元化と記憶容量が向上したことが示唆されたとする。

今回の研究で開発された電子素子は、電子機器の情報処理精度の向上、消費エネルギーの低減を実現する上で重要となることが期待されるという。そして将来的には、コンピュータやスマートフォンなどを含む幅広い電子機器に実装される汎用技術となる可能性があるとしている。