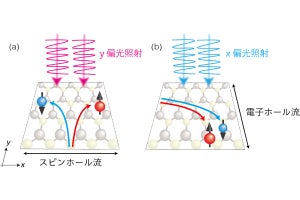

今回の手法としては、量産化を見据え、スパッタリング法を用いて単層MoS2上にSb2Te3を成膜。透過電子顕微鏡(TEM)を用いて、Sb2Te3/MoS2の接触界面にファンデルワールス界面が形成されること、どちらの物質も良好な結晶性を持つ層状構造になっていることが確認されたことから、2つの物質の原子配列が一致していることが示されたとする。

一般的に、集積回路の配線工程では400℃以上の耐熱性が実用化の重要な要件となることから、このSb2Te3/MoS2積層膜構造の耐熱性を調べたところ、ラマン分光法により、熱処理前後にMoS2単層構造が維持されていることが確認されたとするほか、断面TEM画像より、Sb2Te3/MoS2積層膜構造は、450℃の熱処理を経ても良好な結晶性とファンデルワールス界面を維持していることも確認されたとする。

-

(上)低コンタクト抵抗を有するMoS2トランジスタ。左がトランジスタの模式図、右がSb2Te3/MoS2界面を拡大したTEM画像。(下)Sb2Te3/MoS2界面の断面電子顕微鏡(TEM)写真および対応する原子配列 (原論文「Sb2Te3/MoS2 van der Waals Junctions with High Thermal Stability and Low Contact Resistance」の図を引用・改変したものを使用。クリエイティブ・コモンズ・ライセンス(表示4.0国際)) (出所:産総研Webサイト)

さらに、Sb2Te3/MoS2ファンデルワールス界面形成が、トランジスタ特性にどのような影響を与えるかを調べたところ、n型トランジスタ動作を示しつつ、SbやNi、Wなどをコンタクト材料として使用した場合と比べて、Sb2Te3電極を有するトランジスタの駆動電流は4~30倍ほど向上することがわかったという。

このような駆動電流の増大はコンタクト抵抗の低減が主要因であると考えた研究チームが、実際にSb2Te3電極を有するMoS2トランジスタのコンタクト抵抗値を調べたところ、Sb電極を使用した場合のそれと比べて1桁程度低く、またこれまでの世界最小と報告されていたBi電極を使用した場合のコンタクト抵抗値とも遜色のない値であることが判明。SbやBi電極は半導体製造の後工程における高温に耐えられないため、半導体デバイスへの使用には適さないという課題があったが、今回のSb2Te3電極は400℃以上の耐熱性を示しつつ、Bi電極に匹敵する低いコンタクト抵抗値を実現できることが示されたことから、研究チームではBeyond 2nm世代のロジック半導体の実現に寄与するものとなると説明している。

なお、今後については、n型とp型のTMDCトランジスタを直列につないだCMOSを作製することを目指すとしており、その実現のためにも、n型MoS2トランジスタだけでなく、p型TMDCトランジスタにおける低コンタクト抵抗技術の開発が求められるとしている。今回のSb2Te3コンタクト技術は、n型MoS2に対して最適な特性が示されたが、p型TMDCには別のコンタクト材料が必要となるためで、次世代ロジック半導体の実現に向けて、低コンタクト抵抗を有するTMDCによるCMOSの開発を加速させていく計画としている。