インテルは12月5日、今後10年(2030年までに)で単一パッケージ上に1兆個ものトランジスタを集積するという目標に向け、数々の研究結果を国際会議「IEDM 2022」で発表した。今年はトランジスタ誕生から75周年に当たるとのことで、「ムーアの法則が遂げてきたイノベーション」と題したセッションを12月5日9時45分(米国太平洋標準時)から実施する。

「半導体回路の集積密度は、1年半~2年で2倍になる」としたムーアの法則実現に向けて、インテルではさまざまな技術開発を進行中。これまでより10倍高い実装密度を達成した3Dパッケージング技術や、原子3個分の厚さしかない超薄素材を活用した2Dトランジスタの微細化、HPCをさらに高度化するエネルギー効率とメモリの可能性、量子コンピュータの進歩まで、多岐にわたる技術紹介が行われている。

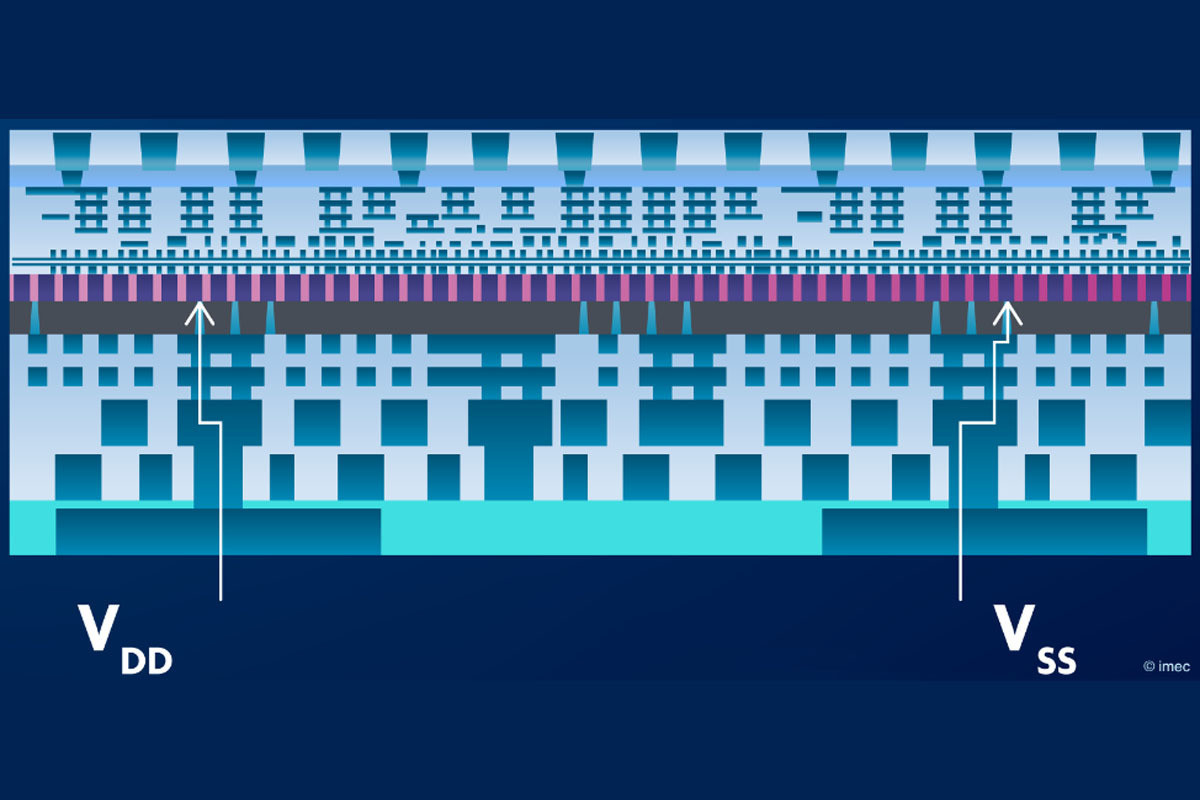

なかでも、3Dパッケージング技術は「ハイブリッド・ボンディング接合」によって3umピッチまでスケーリングしてモノリシックダイと同等のインターコネクト密度を実現。原子3個分の厚みの2D素材で全周ゲート型(GAA)積層ナノシートファブリケーションを実証したほか、室温での漏れ電流も低いトランジスタ・スイッチングの開発にも成功したという。

HPC領域では、トランジスタ上側の垂直方向に配置できるメモリを開発。単一のロジックダイ上にFeRAMを構築できる積層型強誘電体コンデンサのデモを実施した。そのほか、300mmのGaN-on-Siウエハー実現に向けて実行可能な開発指針を構築中。強誘電体ハフニウムデバイスを改良し、最新メモリやトランジスタの開発に用いる業界ツールのサポートを拡大しているとしている。