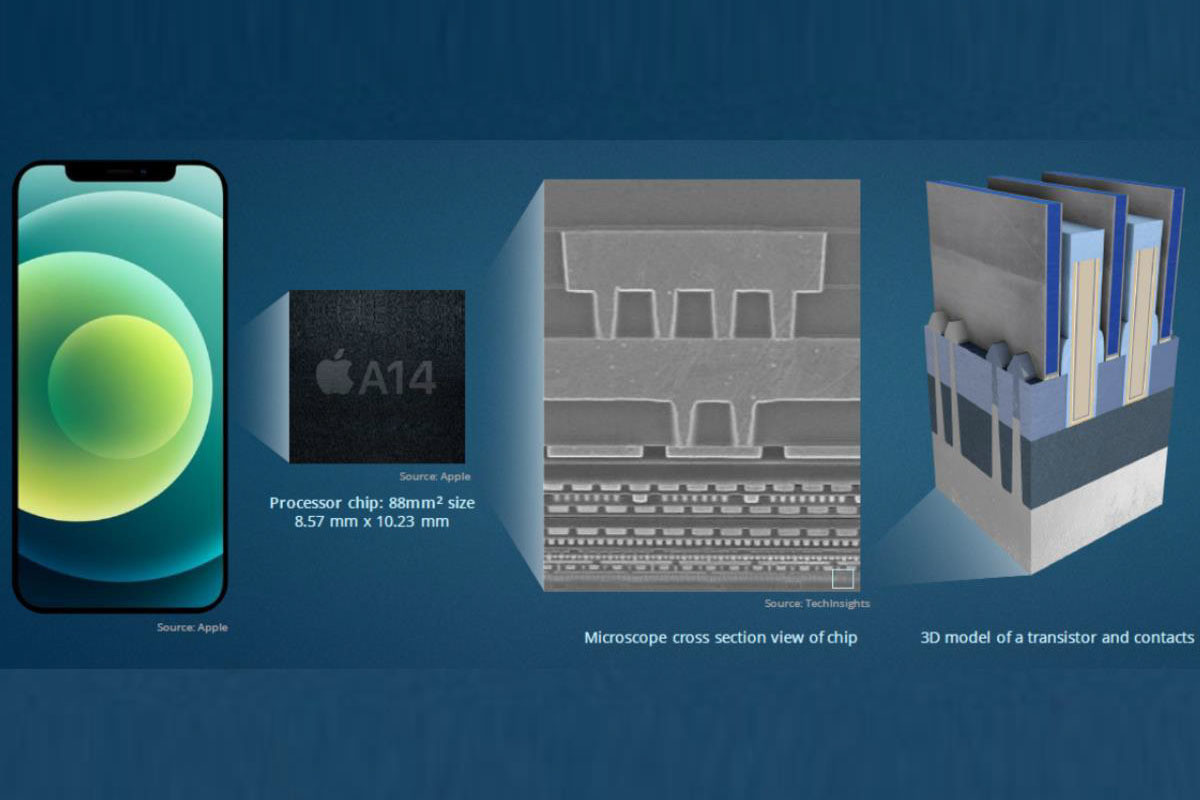

その再構成の内容は、IMC回路の構成要素(ニューロン)を単純化し、それをもとにネットワークを構築するというもので、同構成はRC-Spikeと命名された。RC-Spikeでは、従来式に見られるオペアンプや電流源のようなアクティブデバイスが取り除かれており、それにより電力効率の向上や回路面積の縮小が可能になるとする。

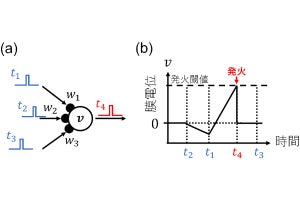

従来式のIMC回路では、キャパシタ電圧の時間発展は区分線形的であり、ニューロンの出力は積和演算と同等となる。IMC回路は、この性質により深層学習の演算が可能になる。

それに対してRC-Spikeでは、時間発展が指数関数的減衰の特性を持ち、出力も積和演算とは異なる。これは、キャパシタに流れ込む電流が、キャパシタの電圧に依存してしまう特性(抵抗結合効果)によるものであり、これによりRC-Spikeは、一般的な深層学習をそのまま演算することはできないという。そこでRC-SpikeをSNNと見なし、SNNの学習アルゴリズムを導出することでこの問題を解決することにしたとする。

標準的ベンチマークであるMNISTとFashion-MNISTを用いて、隠れ層が二層あるRC-SpikeのSNNの学習が行われた。RC-Spikeは、駆動電圧に相当するパラメータVsynによって、動作モードを連続的に変化させることが可能で、Vsynが小さいほど電力効率が向上し、動作がSNN的(抵抗結合効果が大きい)になる。

またRC-Spikeは、抵抗結合効果が強くなる領域(Vsyn~1)においても、一般的な深層学習と同程度の性能を維持することが実現されていることから、これらの結果から、RC-Spikeによって、認識性能を損なわずに、IMC回路を簡略化し電力効率を高めることが可能であるといえるとしている。

なお、今回の研究により、ボトムアップ的アプローチは実用上の大きな利点があることが示されたほか、SNNの新たな活用方法を示したという点も重要だと研究チームでは説明しており、今後は、より詳細なアナログ回路の特性を取り込んだアルゴリズムの開発や、回路試作などを通して、重要社会課題であるAIの電力問題に取り組んでいくとしている。