こうした追加機構を制御装置に組み込むと、バーストエラーに対する耐性を得る代償として、量子コンピュータ自体の速度が劣化する懸念が出てくる。そこで、今回の提案で主要な変更箇所となる要素について数値実験や具体的な回路実装が行われ、その影響が定量的に評価された。その結果、今回の機構は、量子コンピュータの速度にほぼ影響を与えないことが示されたとする。

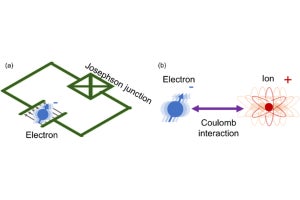

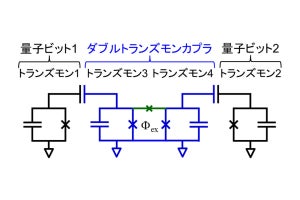

今回は特性が最も調べられていた宇宙線を前提に評価が行われたが、今回の手法はデバイスを問わず、一定の特性を満たす任意のバーストエラーに対して適用可能だとのことで、これにより今回の手法は懸念されてきた同エラーの影響を制御機構の更新のみで軽減できるようになり、大規模な量子コンピュータの実現に貢献することが考えられると研究チームでは説明している。

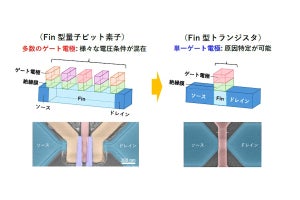

そのため今後の展開としては、(1)提案方式の他量子デバイスへの適用可能性検討、(2)実用的な量子コンピュータシステムとしての実装を可能とする詳細アーキテクチャの設計、という2つの検討を進めていくとしている。1つ目については、今回は実験的にその影響が定量化されていた「宇宙線が超伝導量子ビットに与える影響」に焦点を当てて解析が進められたが、今回の提案の命令セットやエラー推定機構など、多くのデバイスで共通する部分を抽出し、各デバイスに最適化されたアーキテクチャを提案していくとする。

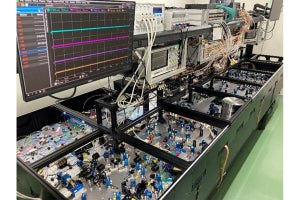

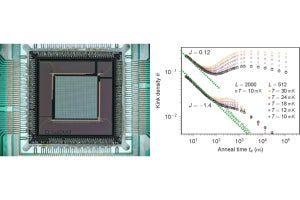

また2つ目については、実用的な規模の量子コンピュータを効率的に設計するには、システムが要求する電力や配線規模の要請を満たす高度なアーキテクチャ設計が必要となり、中でも超伝導量子ビットのような極低温での動作を前提とするデバイスを用いる場合、この要請は厳しいものとなるため、それにも取り組んでいくとしている。

なお、研究チームでは、今回の研究で実施された設計をより緻密化し、こうした制約を満たす高効率な量子計算のアーキテクチャの確立を目指すとしているほか、今回の研究で培われた知見やソフトウェアの基盤を基軸とし、将来的な量子コンピュータを計算機として構成する上で核となる標準的技術の確立を目指すとしている。