PCI Express 7.0は基本変調方式をPAM4のままとし、Flitもそのまま利用しながら、帯域を倍の128GT/secに引き上げるのが基本的なアイディアである。という事は、信号速度そのものはPCI Express 5.0/6.0の32GHzから倍の64GHzに跳ね上がる事になる。これは普通に考えても相当困難なチャレンジであると思われる。実際、質疑応答の中でも、「7.0ではチャネルの長さが相当短くならないか?」という質問が出たが、答えは「仕様策定までには3年ある。その間の技術の進歩でこの辺りを解決できる事に期待したい」という、割と投げっぱなしジャーマン風な答えが返ってきた。

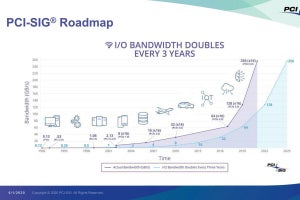

PCI-SIGの想定では、PCI Express 7.0の帯域が必要な時期は2028年頃になるとしており、2025年にPCI Express 7.0の仕様が定まり、そこから実装に入れば丁度間に合う、ということらしい(Photo04)。

-

Photo04:これは、まぁ、おなじみの図である。ただこれ、強いて言えばPCI Express 4.0の仕様策定が遅れた関係で市場の立ち上がりも遅れた面もある訳で、もしPCI Express 4.0がもっと早期に仕様策定されていれば、市場のニーズはこのカーブを上回っていた公算は高い気がする

これが実現すると、x1レーンで32GB/sec、x16レーンでは512GB/secに達する訳で、800G EthernetやAI/ML、クラウド、量子コンピュータなどに広く利用されるであろう、としている(Photo05,06)。

それにしても64GHzである。現在、100G Ethernetなどに向けて56GのPHYは広く利用されているから丸っきり不可能という訳では無いのだろうが、通常のEthernetモジュールの配線は長くても10cm程度。大規模なSwitchの内部であっても配線の取り回しは1~2ft程度だから、これをそのままPCI Expressに持ってくるのは難しいだろう。

今から3年後といえば、丁度800G Ethernetの標準化が終わる頃で、これに先立ってさまざまなMSAが独自規格の800G Ethernetを策定し、OSFP 4.0対応のトランシーバモジュールが市場に出て来はじめている頃だろうから、こうした800G Ethernet向けのアナログ信号技術がうまくPCI-SIGにフィードバックされると良いのだが……。