SkyWaterの130nmプロセスを使うGoogleのプロジェクトでは40個のCARAVELという枠を作り、設計プロジェクトに参加するエンジニア(あるいはエンジニアのチーム)に1つのCARAVELを使わせる。1つのCARAVELは10mm2で、その中にトランジスタなどのコンポーネントを自由に配置し配線で相互接続を作ることがきる。

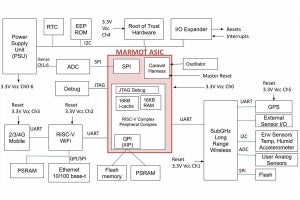

CARAVELは信号の接続や電源の供給などを行うが、この部分は設計済のものが用意されており、それを利用すればよい。CARAVELの枠に自分の設計を入れ、テストチップを作り、Plug & Playの開発ボードに搭載すればLSIの評価ができるようになる。

他の人が設計したCARAVELを使う設計は、15階までできているビルに20階に届くように階を追加するようなものである。この部分の設計者は全部の階について知っている必要は無く、自分の設計する部分だけ分かっていればよい。

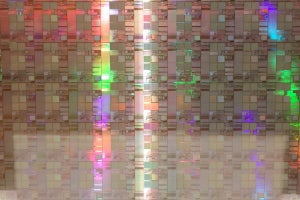

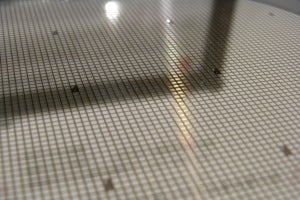

次の図のように、アナログとデジタルの部分の設計を行いCARAVELのユーザエリアに配置する。そしてLSIのファブに製造を依頼する。ファブは300個のWCSP(Wafer Level Chips Size Package)パッケージに入ったユーザーの設計したチップを仕上げて渡してくれる。そして、GoogleはWCSPパッケージに入ったチップを搭載した5枚の評価用ボードを組み上げてくれる。ユーザーの設計が間違っていなければ、評価用ボードに電源、クロック、入力信号などがつながり、ユーザーのLSIが動作を始める。

CARAVELにはロジックアナライザの機能などが組み込まれており、これを使ってユーザーはチップの動作を評価するという手順になる。

SkyWater 130nmプロセスではSRAMのテストチップであるstrive2、PicoRV32を搭載したCaravel1があり、VexRiscvコアを搭載するCARAVEL-Litexが開発中である。そして、2023年にはCARAVEL-Nextを作る予定である。

IPとしてはOpenRAMやFASoC、OpenFPGAが使える。プロセサコアはPicoRV32、Ibexがあり、VexRiscvも使えるようになる。これら以外にもいくつかのコミュニティでRISC-Vコアが作られている。

使える半導体プロセスは現在、SkyWater 130nmプロセスだけであるが、2023年には2番目のプロセスを追加する予定であるという。

Googleは2022年には、4種のウェハの製造費用を援助する予定である。ウェハには最低40個のCaravelハーネスを搭載する。したがって、2022年には合計で160種の設計費用を援助することになる。

チップを製造する設計者はSKY130 Open Source Digital & Analog Design Toolsを使用することができる。そして、チップができると5枚の開発ボードと300個のWCSPパッケージに入ったチップが無償で提供される。

MPW ONEに搭載するすべての設計は公表され、オープンソースライセンスで利用できるものでなければならない。

MPW ONEには45設計の応募があり、MPW-2、-3、-4、-5はそれぞれ56、52、55、77設計の応募があり、いずれもオーバブック状態である。

MPW ONEでは60%の設計が、ハードウェアの設計経験のないエンジニアが応募した設計であり、ソフトエンジニアでもLSIを設計できるようにするという目的は、かなり達成されているといえる。しかし、使用できるIPの種類は非常に少なく、どうやってIPの品揃えを強化するかが課題であると感じる。