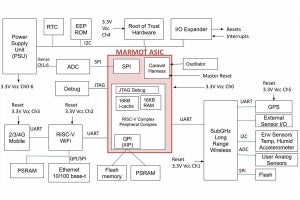

EDAの開発ツールとしてはCadence、Synopsys、Siemensのツールを整備し、IPとしては40nm、28nm、12nmの半導体プロセスの標準IP群を用意する。

-

EDAツールはCadence、Synopsys、Siemensのツールを整備する。ツールはアーキテクチャ検証、論理設計検証、回路設計、物理設計まで一貫したツールを揃える。さらに論理エミュレータ、FPGAプロトタイピング、ボード設計ツールなども揃える。IPはSynopsysの40nm、28nm、12nmの標準IP群(CPU、DSP、DMAC、DDR、PCIe、USB、MIPI、I2Cなど)を整備する

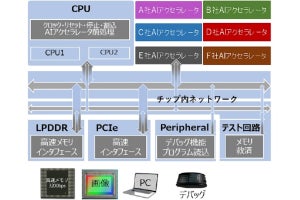

AI-Oneチップには6か所のチップ搭載スペースがあり、各チップに信号を与えたり、チップの出力をモニタしたりするポートが用意されていて、各チップごとに動作をさせて測定を行うことができるようになっている。現在のAI-One評価チップには6社分のAIチップ搭載スペースが設けられている。

そして、現在は、この評価チップを使って各種の実証実験を行っているところである。将来は要求に応じて、AI-Two、AI-Threeと評価チップを作って行く予定である。

-

エッジAI向け評価チップAI-Oneは、6つの評価チップを搭載できる。各拠点は導入している28nmのIPを使って評価プラットフォームを準備する。乗り合い企業(6社)が設計した6種のアクセラレータを1つのプラットフォームに搭載してチップを作り、現在は、作った評価チップを使って実証実験を行っている

設計したチップの論理設計を検証するのには、次の写真にみられるようなCadence社のPalladium論理エミュレータを使用する。

東工大で開発したRISC-VコアでLinuxをブートする過程をPalladiumでエミュレーションするのに要した時間は2分20秒程度で、Palladiumの速度はCPU時間で約1.2Mcycles/s、実行時間で0.9~1.1M cycles/sとなっているとのことである。

-

PalladiumでRISC-VコアでのLinuxのブートをエミュレーションした場合の所要時間は約2分20秒であった。これはCPUのクロックが1MHz程度のチップの実行時間と同程度で、ソフトウェアによるエミュレーションより大幅に速い

拠点の使い方としては、次の図のベンチャーAのように自社のサーバから拠点のツールを使う、ベンチャーBのように端末を接続して使う、ベンチャーCのように拠点に出向いて拠点の端末を使うという形態での利用が可能である。また、AIチップ設計拠点が遠い地方にオフィスがあるベンチャーDの場合はサテライト拠点を使うという使用形態がとれる。

-

ベンチャーAは設計拠点と自社のサーバを接続して使用している。ベンチャーBは自社の端末を拠点のクラウドに接続して使用。ベンチャーCは拠点まで出向いて端末を使用。ベンチャーDはサテライト拠点に出向いて端末を使用している。各種の仕様形態が可能となっている

次の棒グラフは拠点の利用件数を示すもので、2022年の4月の時点で61ユーザとなっている。ユーザの内訳は、企業が43件、大学が11件、国研が6件、その他が1件である。2022年4月の利用件数は166件でユーザ当たりの利用件数は平均で約2.7件となっている。

また、AIチップ設計拠点フォーラムを月1回のペースで開催し、AIチップ、次世代コンピューティング、LSI設計などについて技術情報を共有し、議論する場を持っている。

2022年6月9日訂正:記事初出時、記事の一部にて「Synopsys社のPalladium論理エミュレータ」と記載しておりましたが、正しくは「Cadence社のPalladium論理エミュレータ」となりますので、当該箇所を訂正させていただきました。ご迷惑をお掛けした読者の皆様、ならびに関係各位に深くお詫び申し上げます。