高NA EUVリソは試作機の出荷後3年で量産実用化を目指す

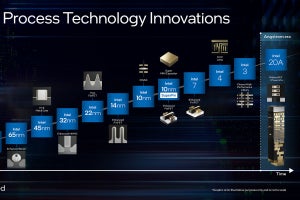

次にEUVリソグラフィの今後のロードマップを見てみたい。2nmプロセスでは、7nm、5nm、3nmに続く第4世代のEUVリソを使ってマルチパターニングを行うことになっており、14Åはその延長線上にある。

しかし、10Åからは従来のNA=0.33のEUVにかわりNA=0.55の高NA EUVリソグラフィが採用される見込みである。imecとASMLはすでにそのためのプロセスを共同開発する「imec-ASML Joint High NA EUV Research Laboratory」をオランダに設置し、高NA試作1号機がASMLより2023年に搬入されることになっている。EUV専用コータデベロッパ(クリーントラック)については、市場を独占している東京エレクトロンが同年に搬入することも決まっている。

ASMLは、最初の量産技術開発に用いられたEUV露光装置「NXE:3100」が2010年に出荷されてから10年後、量産機「NXE:3400」がロジックデバイスの量産ラインに導入された。高NA EUV露光装置の場合は、2023年に試作機(EXE:5000)が出荷されてから3年後の2026年に量産ラインに導入することを目指し、imec-ASMLの共同研究所にて集中的に開発が進められることになっている。

微細化に加えて3D実装でさらなる集積化を実現へ

平面上に並んでいたトランジスタを垂直に積み上げるようにして、集積回路のトランジスタは搭載数を増やす方向にあるが、そこに半導体チップやウェハを積層する3D実装を採用することで、さらなるトランジスタ搭載数の増加を目指す研究が盛んになっている。TSMCが日本に3DIC研究センターを開設したのもこのような事情による。

imecでは、産業界よりも5~8年先の研究を行っており、産業界の実現を早取りすることを目指し、こうした研究を多数のパートナー企業とともに推進している。

半導体製造時の環境負荷低減プロジェクトが発足

imecは最近、新たな研究テーマとして「持続可能な半導体技術およびシステム(Sustainable Semiconductor Technology and Science:SSTSプログラム)」を発足させたことをITF Japan 2021で報告した。

このプログラムは、半導体チップの製造技術(電気エネルギー消費、化学薬品、素材、超純水、ガスなどの消費)が環境に与える影響を予測して、具体的で信頼性の高いモデルと詳細なカーボンフットプリント分析を通して、IC製造時の環境負荷を低減することを目指したもの。製造装置や材料サプライヤ、ファウンドリのような半導体メーカーが研究に参画することを期待していたが、最近になって半導体ファブレスで半導体ユーザーでもあるAppleも参加したこともあり、世界的な脱炭素化(Carbon Neutral)の関心の高さがうかがえる取り組みとして業界に認知されたといえる。

なおimecは、この取り組みを通じて、世界規模の半導体サプライチェーン全体がカーボンフットプリントの削減につなげられるように支援していきたいとしている。