ベルギーimecは2021年11月、日本向け年次技術紹介イベントである「ITF(imec Technology Forum) Japan 2021」を開催し、日ごろの研究成果と今後の計画を発表した。従来は、都内のホテルで開催されてきたが、コロナ禍を踏まえ、バーチャルオンライン形式で行われた。

「ムーアの法則」は、新構造・材料・3次元化で延命へ

「ムーアの法則」が限界を迎えたという悲観的な指摘がすでに前世紀の終わりごろから出回っている。だが、imecは、半導体産業の成長の原動力ともいえる「ムーアの法則」を終わらせないためにプロセス微細化による集積度の向上に懸命に取り組んできた。そして、2020年に至るまで過去50年以上にわたり「ムーアの法則」は継続していると主張している。今後は、超微細化に加えて、新たなデバイス構造や新材料の導入、チップ内のトランジスタ積層や、チップ積層による3次元実装によって「ムーアの法則」は継続すると主張している。

1nm以下のプロセスまで見据えた超微細化技術を研究

まずは、2次元での超微細化に向けた取り組みとしてimecは今回、今後10年先を見据えたロジック半導体のプロセスおよびデバイスの長期ロードマップを示した。

これまで微細化の指標を1nm刻みで表示してきたが、2025年以降はオングストローム(Å)表示の時代になるとして、2025年に「A14」(14Å=1.4nmを意味する)、2027年に「A10」(10Å=1nm)、2029年に「A7」(7Å=0.7nm)に至るロジック半導体プロセス/デバイス実用化のロードマップを示した。

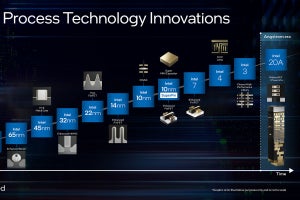

これは、Intelが2021年7月に発表した独自呼称に基づくロジックプロセスロードマップと似たような扱いである(Intelは、2024年に2nmを意味する「Intel 2」、2025年に18Åを意味する「Intel 18A」へ移行し、微細化で先行するTSMCに追い付きたいとしている)。imecの示したロジックデバイスのロードマップには、Industry Timeline(産業界のスケジュール)と記されており、先進半導体企業の生産開始年を示している。

一方、imecではそうした先進半導体企業が生産を手掛けるプロセスよりも数世代先となるプロセスの開発を行うことを長年の研究方針としている。つまり、すでにimecでは1nm以下に微細化したデバイスを実現するためのプロセスや素材の開発を始めているといえる。imecに研究委託した世界中の先進半導体企業は、装置・材料メーカーともども多数の技術者・研究者をベルギーのimecキャンパスに派遣して研究協業している。

なお、これらのロジックプロセスの微細化を示す数値は、以前は、最小加工寸法、最小線幅、MOSトランジスタのゲート長などを示していたが、現在は、各社が微細化の程度を示す独自の指標に過ぎず、実際には集積回路でその長さを示す箇所は存在しない。したがって、TSMCでは、以前より「Nx」(例えば4nmの代わりにN4)」、Intelは最近になって「Intel x」(例えば4nmの代わりにIntel 4)という具合に長さの単位を含まない表記にかわっている。

数値が1世代(技術ノード)ごとに0.7倍になっているのは、1970年にIntelが世界で初めて1K DRAMの生産を始めて以来の伝統で、長さが0.7倍になると面積が1/2になるところからきているが、今では、長さが具体的な物理長を現していないため、面積が1/2になるというわけでもない。

例えば図3で表記されているPPは、ポリシリコン配線ピッチの実際の長さ(nm)、MPは一段目の金属配線層のピッチの実際の長さ(nm)を示している。このように、ロジックデバイスの微細化を示す各社ばらばらともいえる指標は、配線ピッチよりもはるかに小さい数値となっている。

-

図3 imecのロジックプロセス・デバイスの微細化ロードマップ。時間軸は先進半導体企業の生産開始年に合わせてある。imecではすでに1nm(10Å)を超えたプロセスの研究開発を進めているほか、高NA EUVについては、試作機の出荷から量産機の生産導入まで3年を目標としている

世代ごとに変化するトランジスタ構造

ロジックデバイスにおけるトランジスタの構造は、長年にわたるプレーナー構造から微細化に伴いFinFET構造へと置き換わったが、TSMCやIntelでは2nm以降ではGAA(Gate-All-Around)ナノシート積層構造を採用しようとしている。IntelではこれをRibbonFETと呼んでいる。また、Samsungは、他社に先行して3nmからGAAナノシート積層構造(Samsung用語ではMBCFET(Multi Bridge Channel FET))を採用すると宣言している。

imecでは、14Åノードでは、CMOSを形成するためのフォークシート構造(p型とn型ナノシートトランジスタが対をなして配列されており、食事用のフォークに似ているところから命名)を提案して、開発を続けている。10Åでは、CFET(Complementary FET:pチャンネルFETとnチャンネルFETをシリコン表面と垂直に積層)構造を採用しCMOSを構成しようとしている。1nm(10Å)ノードかそれ未満では、1~数原子層の厚みの2D材料を用いてチャネルを形成する「アトミック(原子状)チャネル」を採用する予定である。ちなみに、imecが指す2D材料とは、半導体単層遷移金属ジカルコゲナイド(ダイカルコゲナイド)、化学式MX2で表される材料である。ここで、Mはモリブデン(Mo)やタングステン(W)などの遷移金属元素。Xは、硫黄(S)、セレン(Se)、テルル(Te)などのカルコゲン(16族元素)である。imecは、2D材料と高NA EUVの採用で1nmを超えたプロセス開発の道が開けたとしている。