ちょっと遅くなったが、Intel Architecture Day及びHotChips 33での話を基に、IntelのGPU周りについてのUpdateをお届けしたい。といっても、それほど大きなUpdateがあるわけではないのだが。

Intel Arc

Architecture Dayではサラッと流してしまったので、もう少し細かくご紹介したい。Intel Arcも、この後紹介するPonte Vecchioも、基本となるのはXe-Coreであるが、その構造が実は異なっている。

まずXe-Coreの構造だが、Vector Engineの基本は2018年のHPC Developer Conferenceで発表されたこちら(Photo01)であるが、これはコンセプト的なもので実際のものとはちょっと違うように思われる。実際今回説明によれば、Vector Engineそのものは16個で、それぞれ256bit幅とされており(Photo02)、8bit幅ならEngine1つで32個、32bitで8個、(サポートされるかどうかは不明だが)64bit幅で4つという形だろう。この辺は2020年のArchitecture Dayで説明されたXe-LPのEU(Photo03)に近い。Photo03で言うところのEU(Execution Unit)=Photo01で言うところのVector Engineと考えれば辻褄が合う。つまり一つのXe-coreは16EU相当、と考えれば良い。

-

Photo01: 8bit幅なら64個、32bit幅なら16個、64bit幅なら4つの演算が同時に可能となっている。もっともこれだと、64bit幅では256bitの演算長になってしまっており、数が合わないが。

-

Photo03: 2つのEUが、それぞれ8つのFP/INTの演算ユニットを持つ格好。Thread Controlは2つのEUにまたがる形で動作する。EMはExtended Math ALUの略で特殊演算向け。

ではXe-LPとの違いは? というと、Matrix Engineを搭載した事だ。Matrix EngineはINT8/FB16/FP16の行列演算をサポートするUnit(Photo04)であるが、Photo02にある様にこちらはEngine毎に1024bitの演算が可能である。INT 8なら128演算/cycleとなり、つまり8×8の行列同士の乗算と加算を1cycleで行える、という事だと思われる。

Xe-HPGというか、Intel Arcの第一世代であるAlchemistの最小構成と思われるのがRender Slice(Photo05)で、各々のXe-Coreに一つづつRay Tracing UnitとSamplerが付き、更にRender BackendとかGeometory Engineなどが用意される格好だ。

Architecture Dayでは、このRender Sliceが8つ搭載されたものが示された(Photo06)が例として示された。ただこれが最大構成かどうかは現時点で不明である。実際Roger Chandler氏(VP&GM, Client Graphics Products and Solutions)によれば「現時点ではまだ製品SKUの詳細は公開できない(ので、Photo06が最大構成なのかどうかは答えられない)」としつつ、Xe-GPUの構成はスケーラビリティがあるため、実際の製品の使われ方に応じて自由に変更できるとしている。実際、これが製品SKUをそのまま反映しているかどうかは不明だが、少なくともAlchemistが2種類あるっぽい事を示唆しており(Photo07)、小さい方はGaming Mobile向け、大きい方がDiscrete向けなんて可能性もあるかもしれない。

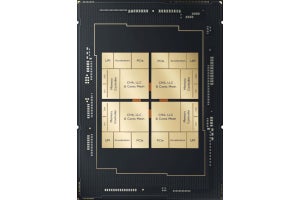

ただ少なくとも8 Sliceというか512EU構成のダイそのものはおそらく実在する。今年6月にKoduri氏自身がそのダイの写真をTwitterに上げており、しかも"DG2-512 B0"なんて但し書きまでなされている訳で、まぁ存在する事そのものは疑う余地がなさそうだ。

話を戻すと、この8 Slice構成はどの程度の性能を持つのか? という話になる。実際にはメモリの帯域とかL2の容量などで性能は変わるからあくまでもざっくりした見積もりであるが、8Slice=512 EU=4096 FP32 Unitとなる。

これと実際の製品の公称値を比較してみると

| AMD: | ||

|---|---|---|

| 製品名 | SP数 | 動作周波数(Base) |

| Radeon RX 6600 XT | 2048 | 1968MHz |

| Radeon RX 6700 XT | 2560 | 2321MHz |

| Radeon RX 6800 | 3840 | 1700MHz |

| Radeon RX 6800 XT | 4608 | 1825MHz |

| Radeon RX 6900 XT | 5120 | 1825MHz |

| NVIDIA: | ||

| 製品名 | CC数 | 動作周波数(Base) |

| GeForce RTX 3060 | 3584 | 1320MHz |

| GeForce RTX 3060 Ti | 4864 | 1410MHz |

| GeForce RTX 3070 | 5888 | 1500MHz |

| GeForce RTX 3070 Ti | 6144 | 1580MHz |

| GeForce RTX 3080 | 8704 | 1440MHz |

| GeForce RTX 3080 Ti | 10240 | 1365MHz |

| GeForce RTX 3090 | 10496 | 1395MHz |

となっており、8 Sliceだと(動作周波数次第ではあるが)Radeon RX 6800 XTとかGeForce RTX 3080あたりと何とか勝負が出来るかどうか、という程度でしかない。余談ながら、GA102系のコアでは1個のSM:Streaming Multiprocessorに128個のCUDA Coreが搭載されているが、うち半分はFP32専用、残りの半分はINT32/FP32共用となっており、なのでINT演算の場合には表のCC数の半分が有効、ということになる。ただDirectXの描画パイプラインはINT32とFP32の混合であり、なので実効CC数というのは表の2/3位を想定しておくのが無難だろう。現実問題として例えばGeForce RTX 3080がRadeon RX 6800 XTと拮抗する性能、というあたりは結構FP32で動く部分が大きいという事でもある。

話を戻すと。そんなわけで8 Slice=512 EUというのはハイエンド向けというにはちょっと厳しいものがある。勿論仮にIntelがこれを3GHzとかでブン廻すことが出来れば、ハイエンド製品として十分な性能が出せるかもしれないが、TSMCのN6がそこまでぶん回せるとも思えない。となると8 Sliceというのはミッドレンジ~ハイエンドの下の方狙いであって、エンスージャスト向けにはもう少しSlice数が多くないと競争力が十分ではない様に思える。この辺りは現実問題としてどの辺をIntel Arcが狙っているか次第ではあるのだが、本気でマーケットを獲るつもりならラフに言っても12 Slice位のモデルが必要な気はする(あくまでメモリ構成とかL2の容量次第ではあるのだが)。

ちなみにメモリ構成などに関しては現時点で全く情報が無い。こちらは製品が出てくるまでお預け、ということらしい。また製造プロセスはTSMCのN6を利用している事は既に明らかになっているが、これはあくまで設計時点において利用できるプロセスのCapacity(どれだけの数を量産できるか)とPerformance、Costを勘案の上で決める、という話であった。

以前こちらで書いたが、Intel 7が予定通りに行けば今年後半に利用できる事にはなる。しかしIntel 7はTSMCのN7と大体同程度で、しかもまずAlder LakeやSapphire Rapids、更には後述するPonte Vecchioにも利用されるから、いくらIntelとはいえこれを供給するのは難しいだろう。そう考えれば、TSMCのN6を利用するのは賢明というか、現実問題としてIntel 7を待っていたら量産開始は来年後半になりかねないから、他に方法は無かったというべきだろう。ただXe-HPGの第2世代(Battlemage)に関しては、もしIntelが毎年1世代づつ新しい製品を投入するとすれば、ぎりぎりIntel 4が間に合うかもしれないというあたり。ただIntel 4の「2023年前半」が1月頭なのか6月末なのかでだいぶ話は変わる訳で、こちらも場合によってはIntel 4あるいはIntel 3にいずれは切り替えるとしても、当面はTSMCのN5あるいはN4という可能性もある(時期的に言えばTSMCのN3が既に利用可能になっている時期ではあり、IntelがこのTSMC N3の予約を既に入れているという話は流れてきているので、あるいはBattlemageはこのTSMC N3の可能性もあるが)。

ついでにいくつかの補足情報も。まずXeSS。これはNVIDIAのDLSS同様に、MLベースのSuperSamplingを行う技法であるが、なんと後方互換性がある、とされた。つまりXeベースの最初の製品であるDG1、あるいはやはりXeベースのGPUを利用するTigerLakeベースのCoreプロセッサでもXeSSは利用できるという話であった。

ただ疑問なのは、これらのコアはMatrix Engineを搭載しないことだ。この場合可能性は2つあり

- CPU側でXeSSに必要なML処理を行う

- Vector Engineで必要なML処理を行う

のどちらかになる。まずCPUに関して言えば、Xeon向けだとCascade Lake以降のCPUはAVX512の一部としてVNNIが実装されているが、コンシューマ向けのCoreプロセッサシリーズでVNNIが利用できるのはTiger Lake以降である(これはAVX512とは別に実装されている)。またIce Lakeの世代にはGNA 1.0というAI/MLアクセラレータが搭載され、Tiger LakeやRocket Lake世代ではGNA 2.0に切り替わっている。これを駆使すれば、あるいはCPUでも処理ができる「かもしれない」が、この場合CPUとGPUの間に猛烈なデータ転送が発生する事を考えるとあまり得策ではないだろう。

なので実際にはおそらくVector Engineの一部をXeSSの処理用に割り当てるという形での実装になるかと思うが、この場合には肝心の描画性能を犠牲にすることになるので、どの程度性能が改善されるのか、ちょっと微妙なところではある。まぁそれでもAMDのFSRの様にMLを利用せずにSuperSamplingを行える技法もあるので、このあたりは実装次第という感じである。いずれ性能を確認してみたいものだ。

またIntelとしてはWorkstation向けのSKUも少なくとも何かしらは考慮しているようだ。現時点で明確にラインナップを分けると明言したわけではないが、「勿論我々はWorkstation向けのマーケットをサポートするし、例えば3DS Maxの様なProfessional Applicationをサポートする」としたうえで、ただそれをどの製品SKUでサポートするかはまだ答えられないものの、Intel Arcそのものはそうしたハイエンド製品をサポートできる能力がある」とはしている。ただこれ、現実問題としてはむしろMobile Workstation向けの統合GPUに、こうしたProfessional Applicationのサポートを追加するというのが先であろう。現在こうした用途では、Mobile Workstation向けのSKUの内蔵GPUを無効化して、NVIDIAのQuadro for Mobile Workstationを搭載する、という形で販売されているものが殆どである。まずはこの用途を内蔵GPUで賄えるようにするのが先で、その先でDiscreteのWorkstationモデルが展開、という感じではないかと思う。

最後にドライバであるが、AMDやNVIDIA同様に定期的なDriver UpdateのRelease Scheduleを考えているとの事。もっともその頻度がどの程度か、は現時点では明らかになっていない。