1nm超プロセスの最有力候補として2D材料をimecが提言

imecは、二硫化タングステン(WS2)のような2次元(2D)材料を用いることでロジックトランジスタの微細化ロードマップを1nmを越えて拡張できることを提案した。

imecでは、これまでも2D材料を300mm CMOSプロセスに統合するための基礎研究を進め、デバイスのパフォーマンス向上に取り組んできた。こうした研究結果のうち4編が論文として今回発表され、そのうちの1つがIEDMのハイライト(注目)論文に選択された。

シリコンベースのMOSトランジスタのゲート長をこれまで以上に縮小しようとしても、短チャネル効果によって特性劣化が引き起こされ、微細化が困難であった。

しかし、ソースドレイン間のチャネルとしてシリコンの代わりに半導体遷移金属ジカルコゲナイド(MX2、WS2やMoS2など)を備えたFETは、これらの短チャネル効果の影響を比較的受けないことが期待されている。このような2D半導体チャネルを備えたFETは、チャネルの厚さに関係なく、より高いキャリア移動度を維持する理論的能力と、原子的に薄いチャネルを作成する能力を併せ持っていることから、ゲート電圧によるチャネルの静電制御を向上することができるという。

imecのプログラムディレクターであるIuliana Radu氏は、「2D FETは、ロジックデバイスのスケーリングロードマップをさらに拡張するための主要な候補と見なされる。imecでは、これらの2D材料を300mmウェハを用いた標準プロセスに採用するように調整した。これは、産業界が2D材料を問題なく採用するための重要な要件である。また、デバイスのパフォーマンスを向上させ、基本的な理解を深める上で、大きな前進を遂げた。その成果をIEDMにて4件の論文として発表した」と述べている。

imecがIEDM 2020で発表した4件の2D材料に関する発表は以下の通り。

- Introducing 2D-FETs in device scaling roadmap using DTCO, Z. Ahmed et al.

- Wafer-scale integration of double gated WS2-transistors in 300mm Si CMOS fab, I. Asselberghs et al.

- Dual gate synthetic WS2 MOSFETs with 120µS/µm Gm 2.7µF/cm2 capacitance and ambipolar channel, D. Lin et al.

- Sources of variability in scaled MoS2 FETs', Q. Smets et al. (IEDM 2020の注目論文に選出)

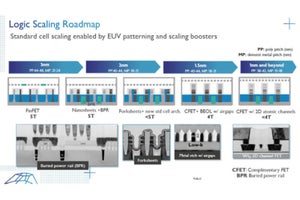

1つ目の2D-FETによるロジックデバイススケーリングロードマップの拡張:設計とプロセス技術同時最適化分析について、論文の筆頭著者であるimecのZubair Ahmed氏は、「imecの設計技術同時最適化(DTCO)フレームワークを使用することで、2D半導体チャネルを備えたトランジスタがロジックスケーリングロードマップをさらに拡張できることを示すことができた」と述べているほか、「2nmでの回路レベルの電力性能領域(PPA)評価により、たとえば、スタックされた2Dナノシート構成のデバイスは、Siベースのデバイスよりも優れており、フットプリントが削減されることが明らかになった」とも説明している。

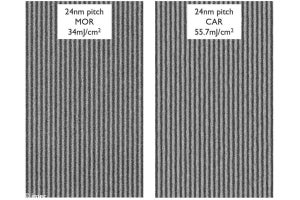

2つ目の300mm Si CMOSファブで作製した2重ゲートWS2トランジスタのウェハスケール集積について、imecの新規ロジックデバイス開発プログラムマネージャーであり、関する論文の筆頭著者であるInge Asselberghs氏は、「今回の研究により、2D FET用のユニークな300mmテストツールが生みだされ、ゲート長が18nmまでのMOSデバイスの製造が可能になった。このテストツールは、チャネルの堆積や転送プロセスなど、さまざまな処理条件の影響を調査するために使用された」と述べている。また研究チームでは、2D成長膜の品質、ゲート誘電体の形成、ドーピング、接触抵抗など、残された課題も特定したとしている。

3つ目の120μS/μm Gm 2.7μF/cm2キャパシタンスと両極性チェネルを備えた2重ゲート合成WS2 MOS電界効果トランジスタについては、論文の筆頭著者であるimecの主任サイエンティストであるDennis Lin氏は、「トップゲートとバックゲートが接続された2D FETは、駆動電流、相互コンダクタンス、サブスレッショルドスイングの点でシングルゲートよりも優れていることが実験的に示された。これは、短チャネル効果を評価するための重要な指標である」と説明。デュアルゲートの概念は、CMOS動作への期待も示すものだとしている。

そして4つ目の微細化したMoS2FETの変動の原因についてimecの主任研究員であり、論文の筆頭著者であるQuentin Smets氏は、「ナノスケール2D FETデバイスの電気特性変動研究として、2Dチャネルの厚さ、2層の縞の存在、2D成長テンプレートなど、さまざまな変動の原因と、電気的性能(主にしきい値以下の領域)に対するそれぞれの影響を調査した結果、2Dベースのチャネルを単一の均一な単分子層に薄くすると変動性が大幅に減少することがわかった。トランジスタをさらにスケーリングするには非常に薄いチャネルが必要になるため、これは有望な結果である」と述べている。