Youtubeで行われたGTC2020の基調講演

2020年は新型コロナウイルスの感染拡大の影響でGTC2020の論文発表はWeb上で五月雨式に実施されたりしているが、Jensen Huang CEOの名物基調講演は、Youtubeでの発表で、日本時間では5月14日の22:00からという開催となった。

発表の目玉は、ハイエンドのAmpere(アンペア)アーキテクチャベースの「NVIDIA A100 GPU」である。ただし、米国の次期エクサスケールスパコンのアクセラレータとしては、El CapitanとFrontierがAMDのRadeon Instinct系のCDNAアーキテクチャのGPUを使い、AuroraはIntelのXeアーキテクチャの新GPUを使うことになっており、残念なことに米国の次期トップ3となるエクサスパコンではNVIDIAのAmpereの出番は無い。

第3世代Tensorコア

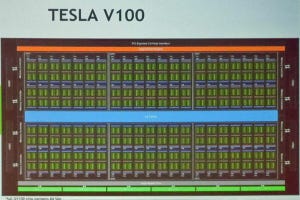

しかし、GTC2020での発表を聞くと、A100は素晴らしいGPUである。A100はTSMCのカスタム7nmプロセスを使い540億トランジスタを集積し、第3世代のTensorコアを搭載している。

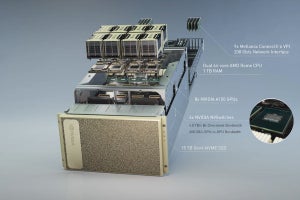

このTensorコアは疎な係数行列を扱う場合は、最大2倍の実効演算性能が出せる。そして、MIG(Multi Instance GPU)という機能で、A100を最大7個の仮想GPUに分割して使用できる。推論などの負荷が軽めの処理では最大7人のユーザで1個のGPUをシェアできるので、データセンターには美味しい機能である。そして、A100では第3世代のNVLinkとNVSwithになり、データバンド幅が2倍に改善されている。

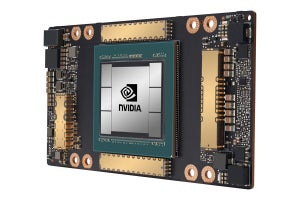

以下の画像右側の写真がA100チップを搭載するモジュールであるが、目を惹くのはHBM2メモリが6個になっている点である。これでメモリバンド幅が約1.5倍になる。それからA100を取り囲むように配置されている金色の細長いICが見えるが、これらはVicorの48V給電の電源ICである。

なお、上下のHBM2の間にGPU LSIの配線パターンのようなものが見えるが、これはフェイクで、後に出てくるEGXボードの写真のように、本物はチップの情報をレーザーマーキングした黒いシリコン面が見えるだけである。

-

A100は540億トランジスタを集積し、第3世代のTensorコアを搭載している。疎行列の圧縮演算機能を使うとTF32で最大312TFlopsの演算性能を持つ。デバイスメモリはHBM2が6個となり、1.6TB/sのバンド幅となった(このレポートのすべての図は、GTC2020のHuang CEOの基調講演の発表スライドのコピーである)

TF32という新しい数値表現

A100 GPUの開発にあたってNVIDIAはTF32という新しい数値表現を作った。次の図に示すように、TF32ではExponentは8bit、Mantissaは10bitで、これにSignの1bitを加えても19bitで、32bitには大分足りない。バイト単位でアクセスするメモリには中途半端であるので、メモリの使用量としては32bit単位と変わりはないと思われる。しかし、積和演算などの回路としては19bitだけ計算すれば良ければ、簡単になる。

そして、TF32はExponentの部分はFP32と同じで、Mantissaの部分はFP16と同じという構造になっている。つまり計算の精度的にはFP16と同じで、数値の表現範囲の点ではFP32と同じということになっているところがミソである。

ニューラルネットでは、すべての入力に信号が入っているとは限らない。その時に、入力に掛ける重みをゼロにしてやれば結果は正しいが、GPUとしてはゼロを掛けるという無駄な計算を行うことになってしまう。A100のTensorコアは、無駄な演算をやる演算器に有効な計算をやらせるようにして、最大2倍に実効性能を上げられるようになっている。

また、TensorコアはFP16、INT8に加えてTF32、BFLOAT16、TF32(テンソルコア用の32bit浮動小数点数)形式の数値も扱えるようになっている。