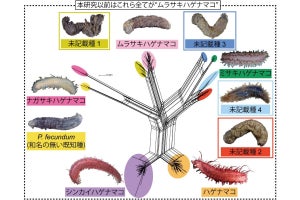

英Armは現地時間の2月20日、同社のサーバ向け専用となる新しいプロセッサIP「Neoverse N1」および「Neoverse E1」を発表した(発表資料)(Photo01)。

-

Photo01:サーバ向けでは、IPではなく"プラットフォーム"という扱いになる模様。なぜN1とE1なのか考えてみたが、もし将来、エントリ向けにNeoverse Oシリーズが投入されると考えてみると、Cortexと同じネーミングセンスだったという事なのだと思われる

同社は2018年10月におけるNeoverseの発表の際に、2019年にAresプラットフォームが投入されることを明らかにしていたが、今回発表されたNeoverse N1がまさにこのAresプラットフォームに相当することになる。

-

Photo02:元々のロードマップでは世代ごとに30%以上の性能アップとしていたが、Cosmos→Aresでは60%の性能改善となる。余計なお世話かもしれないが、この後のAres→Zeusがきつくならないのだろうか?

実際にはAresだけではなくHeliosプラットフォームも同時期に出る事が予告されており(Photo03)、こちらがNeoverse E1になる訳だ。

-

Photo03:Arm TechConにおけるテクニカルセッションの資料から抜粋したグラフ。2018年時点ですでにリリース扱いになっており、OEMには提供を開始していた事が判る。タイミング的なものを考えると、当然そうなる

Neoverse N1の正体 - Cortex-A76とどこが違うのか

さて、そのNeoverse N1であるが、Drew Henry氏(SVP/GM, Infrastructure Business Unit)はNeoverseの発表の際に、「AresはCortex-A76と異なる」と説明しており、実際の製品としても別のものとなる。

ただし、ベースとなるアーキテクチャというか、基本構成そのものはCortex-A76である。これは実際、「Arm Neoverse N1 CPU Technical Reference Manual Revision r3p1」のリンク先にあるドキュメントが、「Arm Cortex-A76 Core Revision: r3p1 Technical Reference Manual」と記載されていることからも明らかだ。

そういう経緯もあり、Neoverse N1はRevision r3p1という扱いになるが、その前のRevision r3p0との違いはMIDR_EL1(Multiprocessor Affinity Register)というRead Only Registerの初期値が変わっているだけで、見た目で言う限りCortex-A76とまったく違いが無い。

では同一のコアか? というとそういうことも無く、微妙に違いがある。ArmのWebサイトにあるNeoverse N1(Photo04)とCortex-A76(Photo05)を比較すると、まず異なるのがL2のサイズである。

-

Photo05:こちらはCortex-A76。ここで「64KB I-cache Parity」の右にある「64KB L1 I-Cache ECC」は「64KB L1 D-Cache ECC」の間違いだと思われる

Cortex-A76は256KB/512KBの選択だが、Neoverse N1ではこれに1MBのオプションが追加された(L3がクラスタ最大4MBなのは同じ)。また、Cortex-A76は1クラスタあたり最大4つのCPUとなっているが、Neoverse N1の場合はクラスタあたり最大4つに加え、DirectConnectの接続にも対応している。

またクラスタからInterconnectへの接続が、Cortex-A76では1x or 2xの128bit AMBA ACEなのに対し、Neoverse N1では256bit AMBA 5 CHIのDirect-Connectに変更になっている。これは対応するInterconnectの違いによるものだろう。

細かい所ではさらにいくつか違いがある。まず対応するPA(Physical Address)がCortex-A76では40bit(1TB)なのに対し、Neoverse N1では48bit(256TB)まで拡張されている。

対応している命令セットも、基本がArmv8.2-A+Cryprography extensions+RAS extensionsなのは変わらず、これにARMv8.3-AのLDAPR命令が追加されているというものだが、Neoverse N1ではこれに加えてSPE(Statistical Profiling Extension)とArmv8.4AのDot Product Instruction、さらにArmv8.5A(Security Vulnerabilities Mitigations)のPSTATE SSBSbitも追加されている。

SPEはArmv8A(厳密にはArmv8.2A)の拡張として定義されたもので、名前の通り実行時のプロファイリングを行うための機能拡張。Armv8.5AはSpectre/Meltdownから始まった一連の脆弱性に対応するための拡張である。これらがCortex-A76に実装されていないのか? というと結構怪しい感じで、実装はされているが検証およびソフトウェアのサポートがNeoverse N1のリリースで間に合ったというあたりで、後追いでCortex-A76でもサポートされる可能性はありそうだ。

ただ逆に違いはこの程度に留まるようだ。4命令同時デコード/8命令同時発行のパイプライン構造(Photo06)は同一であるし、48 entry L1/1280 entry L2 TLBやin-flightで48LD/72 ST/20 outstanding Non-Prefetch missといった構造も特に変化はないようだ。

-

Photo06:Load/StoreはAGUが2つ搭載され、2命令同時発行が可能。FPU/VectorはNEONが2ポート用意され、FMUL/FADD/ALUに関しては同時2命令発行可能。Integerについては、ALUが3つ(うち1つはMAC/DIV共用)ということで合計8命令の発行が可能である

説明によればSystem Cacheは「22ns load to use in typical system」とされているが、もともとCortex-A76がDynamIQ経由でL3をアクセスするときのLatencyが26~31cycleとされているから、仮にシステムの動作周波数が1.4~1.5GHzあたりだと仮定すれば大体22ns前後に収まることとなる。

スマートフォン向けに比べると動作周波数が低めと仮定しているのは、最大で128コアまで集積される事を考慮しているためで、この枠だとコアあたり2W程度に動作周波数を抑える必要がある。

スマートフォン向けの場合、負荷に応じて細かく動作周波数を変更する関係でトップだと2GHz超えが当たり前だが、サーバ向けの場合は長時間にわたり一定の負荷が掛かりっぱなしになる事が多い。2W枠だと恐らくは1.5GHz前後というのは妥当な数字ではないかと思う。

ちなみにPhoto08もArm TechConにおけるスライドであるが、Photo07に出てきた構成がシステム的にどんなシステムになるか、をまとめたものである。

-

Photo08:こちらはNeoverse E1も含めた構成であり、Photo07と順序が違うが、Network StorageやSecurity(Smart Offload)なら8~32コア程度、Edge Compute(5G Wireless access)なら最大64core程度、Hyperscale DatacenterやHPC向けだと最大128coreという形だ

ArmはあくまでもProcessor IPとMeshを提供するところまでで、その先についてはそれぞれのベンダ任せになる、という形になる訳だが、逆にそこがベンダの差別化の要因となっていく形だ。

ちなみに主要なDatacenter向けアプリケーション(Photo09)の性能として、Cortex-A72比で

- NGINX:2.5倍

- OpenJDK:1.7倍

- MemcacheD:2.5倍

- MySQL:1.6倍

- DeepBench:6倍

- DPDK:最大2倍

- Open vSwitch:1.6倍

といった数字が示されている。