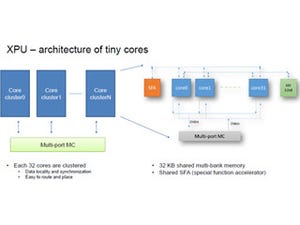

電力制御は、個々のCPUコアとL2キャッシュごとに電力状態を指定することができるようになっている。CPUの電源は、ブロックヘッドスイッチ(BHS)、あるいはロードロップアウト・レギュレータ(LDO)を経由して供給されており、軽スリープ、電圧保持、レジスタ保持、昏睡という4種のステートがある。軽スリープはCPUクロックの停止、電圧保持はレジスタとキャッシュは状態保持、レジスタ保持はキャッシュは保持せず、レジスタ状態だけを保持する。そして昏睡はレジスタもL1キャッシュの状態も保持しない。

L2キャッシュもCPUと類似のパワー状態をとることができる。それに加えて、L2キャッシュはCPUがアクティブでもL2キャッシュアクセスがない場合は自動的にクロックゲートする。また、両方のCPUが低電力ステートの場合は、保持状態、あるいは昏睡状態に入ることもあるという。

Centriq 2400は48 CPUコアと24 L2キャッシュを持つので、72か所の電源制御を行っていることになる。これは、かなりきめ細かい制御であり、省電力の効果が大きいと思われる。

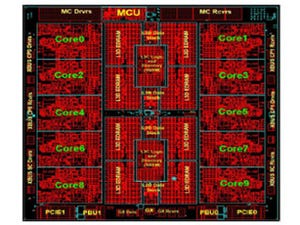

Centriq 2400 SoCはFalkor Duplexを24個と大容量のECC付きL3キャッシュ、6チャネルのDDR4メモリコントローラ、32レーンのPCIe Gen3ポート、DMA、SATA、USBなどをサポートするサウスブリッジを持ち、これらをQSBリングバスで接続した構成になっている。パッケージは55mm角のLGAである。

L3キャッシュは、QoS制御ができ、次の図の右側の絵のようにWayベースのアロケーションができるようになっている。なお、富士通の京コンピュータのSPARCプロセサも、ずっと昔から、このようなWayベースのキャッシュアロケーションを行っている。

Centriq 2400はメインメモリのデータを圧縮している。このような圧縮を行うプロセサは無いわけではないが、比較的珍しい。可能な場合は、128バイトのデータを64バイトに圧縮してメインメモリに格納する。圧縮したデータの伸長は2-4サイクルででき、オーバヘッドは小さいという。

データを圧縮すると、メモリをアクセスするデータ量が減り、実質的なメモリバンド幅が向上する。また、メモリアクセスに必要な消費電力が減少する。しかし、その効果はワークロードの性質によるとのことで、具体的な改善の数値には言及されなかった。

|

|

|

Centriq 2400は、可能な場合には、DRAMメモリへの128バイトの書き込みデータを64バイトに圧縮する。これにより、使用するメモリバンド幅が減り、メモリアクセスのエネルギーも減らすことができる |

まとめであるが、Centriq 2400は業界初の10nmプロセスで製造されるサーバ用CPUである。Qualcommの第5世代のプロセサコアであり、サーバ用に最適化されている。アーキテクチャはARMv8であり、性能、性能/Wは業界の最先端を狙っている。

Centriq 2400は、マイクロソフトのProject Olympusでの採用プロセサの1つであり、Open Compute ProjectにCentriq 2400を使うサーバの設計を提出しているという。そして、Centriq 2400上で、すでにWindows Serverといくつもの版のLinuxが動作しており、2017年末までに量産を開始するスケジュールは順調に進んでいるという。

|

|

|

まとめと現状。Qualcommの第5世代のプロセサコアで、サーバ用に最適化されたARMv8アーキテクチャのSoCである。すでに、Windows Serverやいくつもの版のLinuxが動作しており、2017年末の量産開始のスケジュールは順調に進んでいる |

業界最先端の性能と性能/Wを狙った設計とのことであるが、Hot Chips 29においては、具体的な性能や消費電力は発表されなかった。マイクロソフトのProject Olympusでの採用候補になっているが、GoogleやFacebook、Amazonなどの大手クラウドサービスセンターにどこまで食い込めるかが、その真価がいよいよ試されることになる。