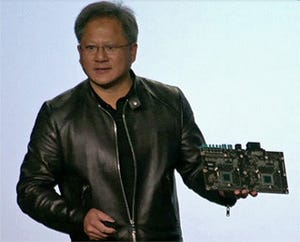

NVIDIAは、現地時間の5月8日~11日まで米カリフォルニア州San Joseにおいて、GPUを利用した深層学習やAIなどをテーマとした技術者向け会議「GTC 2017」(GTC:GPU Technology Conference)を開催した。3日目の5月10日には、NVIDIAの創始者兼CEOのジェンスン・ファン氏がキーノートに登壇した。

GTCは、スーパーコンピュータなどのHPC(High Performance Computing:高性能コンピューティング)向けの技術会議として2009年にスタートし、その裾野を機械学習や深層学習、AIへと広げてきた。特に、2012年からの5年間は、CPUの性能向上が鈍化したこともあって、GPUを利用した並列演算に注目が集まるとともに、いまや米国内では大学でいちばん学習したいテーマとなった「AI」(人工知能)では、GPUが不可欠となるなど、GPUコンピューティングは、ずっと身近なものになった。

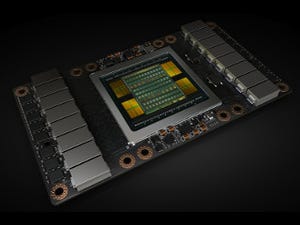

次世代GPUアーキテクチャ"Volta"ベースのTesla V100をお披露目

さて、キーノートスピーチの目玉として、NVIDIAの次世代GPUアーキテクチャとなる"Volta"(ヴォルタ:開発コードネーム)が公開された。"Volta"は、これまで"グラフィックスプロセッサ"の汎用並列処理性能を向上させてきた流れから飛び出し、AIや深層学習へアーキテクチャレベルで最適化を図るアプローチに打って出た。

Tesla V100は、CUDAコアに加え、テンソル(Tensor:多次元配列)演算処理のための専用コアであるTensorコアを統合し、機械学習におけるトレーニングや推論の性能向上を大幅に引き上げることが可能だ。NVIDIAは"Volta"アーキテクチャにおいて、Tensorコアを利用した深層学習処理への最適化を図るべく、新たな命令セットを追加するなど、大幅なアーキテクチャ変更を施している。

例えば、従来のGPUアーキテクチャにおいて、4×4のマトリックス演算を行なう場合、1階層ごとに演算処理を行ない、多次元配列演算を完成させる必要があったが、Tensorコアを採用したVoltaアーキテクチャでは、4×4のマトリックス演算を行なう専用ユニットを搭載することで処理の高速化を実現する。

|

|

|

|

4×4のマトリックス演算を行なう専用ユニット「Tensorコア」を搭載することで、Googleの深層学習フレームワークとなるTensor Flowでは、Pascal世代のGPU利用時に比べ、12倍の性能向上を果たす |

Googleの深層学習フレームワークとなるTensor Flowでは、Pascal世代のGPU利用時に比べ、12倍の性能向上を果たすという。このTensorコアを、Tesla V100に搭載されるGPUコアの"GV100"では、SM(Stream Processor)ごとに8基、合計640基のTensorコアを統合し、最大120TFLOPSのTensor演算性能を備えるとしている。

GV100では、TSMCの12nm FinFETプロセス「12nm FFN」で製造され、211億トランジスタで5,120基のCUDAコアを統合、7.5TFLOPSの64bit浮動小数点演算性能(FP64)、15TFLOPSの32bit浮動小数点演算性能(FP32)を実現。メモリには、4,096bitインターフェースで900GB/sの帯域を実現するHBM2メモリを16GB搭載するほか、GPU間やCPUとの接続に利用されるNVIDIA独自のインターコネクト技術NVLinkも300GB/sの第2世代へと進化を果たしている。

これにより、Tesla V100では、HPC用途の汎用演算において、Pascal世代比で1.5倍の浮動小数点演算性能を実現するほか、深層学習のトレーニングでは12倍、推論では6倍のテンソル浮動小数点演算性能を実現するとしている。なお、GV100のダイサイズは815平方mmと、半導体の露光限界ギリギリのサイズで、フアン氏によれば「30億ドルの予算をかけて開発されたチップである」という。

| GPUコア | GK110 | GM200 | GP100 | GV100 |

|---|---|---|---|---|

| アーキテクチャ | Kepler | Maxwell | Pascal | Volta |

| トランジスタ数 | 71億個 | 80億個 | 153億個 | 211億個 |

| ダイサイズ | 551平方mm | 601平方mm | 610平方mm | 815平方mm |

| 製造プロセス | 28nm | 28nm | 16nm FinFET | 12nm FFN |

| SM | 15 | 24 | 56 | 80 |

| TPC | 15 | 24 | 28 | 40 |

| SMあたりのFP32コア | 192 | 128 | 64 | 64 |

| FP32コア合計 | 2880 | 3072 | 3584 | 5120 |

| SMあたりのFP64 CUDAコア | 64 | 4 | 32 | 32 |

| FP64コア合計 | 960 | 96 | 1792 | 2560 |

| SMあたりのTensorコア | - | - | - | 8 |

| Tensorコア合計 | - | - | - | 640 |

| GPU Boostクロック | 810/875MHz | 1114MHz | 1480MHz | 1455MHz |

| FP32 TFLOPS(ピーク時) | 5.04 | 6.8 | 10.6 | 15 |

| FP64 TFLOPS(ピーク時) | 1.68 | 2.1 | 5.3 | 7.5 |

| Tensorコア TFLOPS(ピーク時) | NA | NA | NA | 120 |

| Texture Units | 240 | 192 | 224 | 320 |

| メモリインタフェース | 384-bit GDDR5 | 384-bit GDDR5 | 4096-bit HBM2 | 4096-bit HBM2 |

| メモリ容量 | 12GB | 24GB | 16GB | 16GB |

| L2キャッシュ | 1536KB | 3072KB | 4096KB | 6144KB |

| SMあたりの共有メモリ | 16KB/32KB/48KB | 96KB | 64KB | 最大96KB |

| 合計レジスタファイル | 3840KB | 6144KB | 14336KB | 20480 KB |

| TDP | 235W | 250W | 300W | 300W |

またNVIDIAは、Tesla V100を8基搭載し、960テンソルTFLOPSの演算性能を実現する。深層学習向けサーバー「DGX-1 with Tesla V100」の受注を開始した。これはすでに提供中の「DGX-1」のアクセラレータをTesla V100に置き換えたものになる。供給が開始される2017年第3四半期までは、PascalアーキテクチャのTesla P100を搭載した現行製品を提供し、後日Volta版と交換する無償アップグレードにも対応する。価格もPascal版と同じ149,000ドルに据え置かれている。

さらに、スタートアップや個人用の深層学習向けサーバーとして、2CPU構成で4基のPCI Express版のTesla V100を搭載する「DGX STATION with Tesla V100」を発表した。価格は69,000ドル。このほか、クラウド企業や研究機関用に、GPUクラウドサーバーの「HGX-1 with Tesla V100」も追加。用途や規模に応じて、2CPU:8GPU、2CPU:4GPU、1CPU:2GPUの構成を選ぶことができる。