SFDRを制限するその他の要素

SFDRを減少させる可能性があるもう1つの要素は、外部ノイズがADCのアナログ入力またはクロック入力に加わるようなシステム設計です。さらに、システムのボードレイアウトを慎重に行わないと、ADCのデジタル出力が入力に戻ってしまう恐れがあります。外部ノイズが、ADCのリファレンス、電源、またはグランドなどのドメインに加わる可能性もあります。ノイズが十分に大きくて半周期的なものである場合は、SFDRを制限する望ましくないスプリアスとして、基本周波数やADCのアーキテクチャとは無関係にシステムの周波数ドメインに現れることもあります。

GSPS ADCの将来?

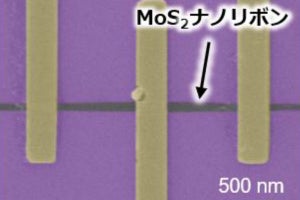

これまでシステム性能を制限していたインターリービング・アーチファクトのない、優れた広帯域SFDRのGSPS ADCが使用できるようになりました。AD9860はデュアルチャンネル、14ビットの1GSPS ADCで、1GHz入力で78dBcのSFDRを実現します。AD9625は12ビットの2GSPS ADCで、1GHz入力での標準広帯域SFDRは80dBcです。

SFDRはGSPSやADCの重要な性能指標です。広帯域SFDRは、通常、基本周波数の第2または第3高調波によって制限されます。シングル・モノリシック・パイプラインADCやその他の先進的アーキテクチャは、高性能GSPSコンバータの新たな世界を開いています。従来のGSPSクラスのADCアーキテクチャでは周波数ドメインにインターリービング・スプリアスが見られましたが、これら新たなアーキテクチャではそのようなことはありません。

広帯域応答が求められるアプリケーションでは、これらのアーチファクトの特定、プランニング、除去が問題となることが予想されます。新しいソリューションはこれらのシステム上の問題を解決し、広帯域スペクトル全域にわたって最先端のSFDR性能を提供します。

参考文献

・W. Kester, "Understand SINAD, ENOB, SNR, THD, THD + N, and SFDR so You Don't Get Lost in the Noise Floor," MT-003 Tutorial, www.analog.com/static/imported-files/tutorials/MT-003.pdf

・M. Looney, "Advanced Digital Post-Processing Techniques Enhance Performance in Time-Interleaved ADC Systems," Analog Dialogue 37-8, August 2003

・W. Kester, Analog-Digital Conversion, Analog Devices, 2004, ISBN 0-916550-27-3, Chapter 6; also available as The Data Conversion Handbook, Elsevier/Newnes, 2005, ISBN 0-7506-7841-0, Chapter 2

・W.C. Black Jr. and D.A. Hodges, "Time Interleaved Converter Arrays," IEEE International Conference on Solid State Circuits, Feb. 1980, pp. 14-15

・W.C. Black Jr. and D.A. Hodges, "Time Interleaved Converter Arrays," IEEE Journal of Solid State Circuits, Dec. 1980, Volume 15, pp. 1022-1029

・J. Harris, "The ABCs of interleaved ADCs," EDN Network, Feb. 17, 2013,www.edn.com/design/analog/4407107/3/The-ABCs-of-interleaved-ADCs

著者プロフィール

Ian Beavers

Analog Devices(ADI)の高速コンバータ・チームに所属するアプリケーション・エンジニア。

1999年入社。

ノースカロライナ州立大学で電気工学の学士号を、グリーンズボロのノースカロライナ大学でMBAを取得。

ADIのオンライン・テクニカル・サポート・コミュニティ「EngineerZone」の高速ADCサポート・コミュニティのメンバーでもある