狭帯域SFDRを外挿して広帯域SFDRを得ることは可能ですか?

そのシステムにとって問題になるのが狭帯域のスペクトルだけであれば、バンドパス・アンチエイリアス入力フィルタを使って、対象帯域外の高調波やアーティファクトを除外することができます。一部のアプリケーションでは、フィルタによって除去したこの周波数帯内の信号を観察する必要がない限り、この方法が有効です。しかし、広帯域シグナル・アクイジション・システムにこの方法を用いることはできません。一部のデータシートでは、ADCの全入力帯域幅よりはるかに狭い間隔でスライスした帯域幅に対してADCのSFDRを規定していることもあります。

通常、狭い帯域幅のSFDRを外挿すれば、より広い帯域幅やFs/2の全ナイキスト帯域にわたる性能が分かると考えることはできません。これは主に、基本周波数の狭帯域に関する周波数プランニングが、高次高調波を対象周波数域から除外するために意図的に確立されたものであることが理由となっています。このフィルタを無くすと、これらの高調波や他のスプリアスが、システム内に見られる広帯域SFDRの一部となります(図2および図3)。

差動入力ADCのSFDRが、他のフロントエンド・システム・コンポーネントの影響を受ける可能性はありますか?

ほとんどの高速ADCは差動入力構造を使用しており、この構造は同相ノイズ除去能力に優れています。しかし、この利点を生かすには、多くのアクイジション・システムにおいて、ADC入力の前段でシングルエンド信号を差動信号に変更する必要があります。受動バラン/トランス、およびアクティブ・アンプは、シングルエンド信号から差動信号への変換プロセスのための主要な選択肢です。システムのこの部分には数多くの高性能コンポーネントを選ぶことができますが、最良のソリューションであっても差動信号に何がしかのアンバランスが生じて対象信号に歪みを発生させ、ADC全体でのSFDRを減少させます。

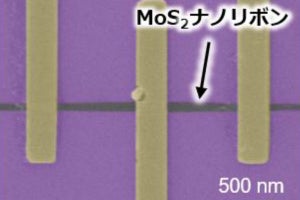

ADCフロントエンドで差動入力信号の両側入力間に生じる位相不整合は、基本信号の高調波の電力を増大させます。これは、差動信号の一方が、周期を基準として一定の位相分だけ他方より時間的に進んでいる時に発生する可能性があります。この状態を図4に示します。図では、差動ペアの一方の周期位相が他方よりわずかに進んでいます。

|

|

|

図4 この場合、バランの出力には、ADCの差動入力に対して数度の位相不整合があります。この結果、FFTの第2高調波は差動入力の位相が完全に整合している場合より高くなり、結果としてSFDRに悪影響を与えます |

差動信号アクイジション・システムのフロントエンドで生じ得るもう1つのアンバランスは、振幅の不整合です。差動信号の一方のゲインが他方と異なる場合、ADC入力は一方が相対的に大きく、他方が小さくなります。これは基本信号の全電力を減少させるもう1つの要因で、SFDRのdBc値は減少します。差動入力間に2dBの振幅不整合があると、入力信号の最大電力は1dB減少します。フロントエンド信号品質に関するこれらの問題は、ADCのSFDRを減少させ、システム全体の信号解読能力を低下させる恐れがあります。