米ブロードコム プロセッサ & ワイヤレスインフラストラクチャグループ シニアディレクターのクリス・オライリー氏 |

ブロードコムは5日、都内で記者説明会を開催した。同社が10月15日(米国時間)に発表した、ARM 64bitプロセッサ(ARMv8-A)採用のネットワークプロセッサのアーキテクチャについて、米ブロードコム プロセッサ & ワイヤレスインフラストラクチャグループ シニアディレクターのクリス・オライリー氏が説明を行った。

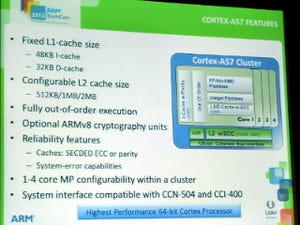

ARMは、すでにARMv8-Aに対応したプロセッサ設計であるCortex-A53/A57を発表している。ブロードコムのプロセッサコアは独自設計のものだが、アーキテクチャにARMv8-Aを採用しているため、同じ命令セットが利用できる。このプロセッサは、アウトオブオーダー実行、スーパースケーラーで、同時4命令発行、同時4スレッド実行というマイクロアーキテクチャを採用する。

10月に発表した計画では、ブロードコムがARMのアーキテクチャライセンスを活用して、プロセッサのパイプラインやキャッシュ構成などをブロードコム自身が独自に設計するとしている。

製造は台湾TSMCが担当し、16nmプロセスのFinFETプロセスを採用。製品の動作クロックは3GHzを予定する。具体的な製品の出荷時期は公開していないが、今後1年ぐらいが出荷のターゲットだと思われる。

|

|

10月に発表した次期ネットワーク用プロセッサSoCの概要。16nmFinFETを採用しクロック周波数は3GHz。アウトオブオーダー、スーパースケーラーで4命令発行可能、4スレッド実行が可能な独自実装のARMv8プロセッサを開発する |

ブロードコムは、このプロセッサアーキテクチャを持つコアをベースに、パケットエンジンや暗号化などのネットワーク処理用の各種アクセラレータ、ネットワークインタフェースなどを統合した1チップのSoCを開発する予定だ。開発には、ARMも協力しており、ARM 64bitをベースとした最初のネットワークプロセッサになるという。

ARMのアーキテクチャには、ARMv7やARMv8がありこのうち64bitのアプリケーションプロセッサ向けのARMv8-Aは、64bitモード(AArch64と呼ばれる)とARMv7互換のAArch32から構成されている。

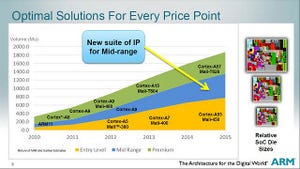

ARMは2011念に64bitアーキテクチャを発表。当初の参入分野としてサーバーやインフラ向けのネットワーク機器をターゲットにした。今回のブロードコムの製品は、こうしたARMの方向に沿うものだ。

オライリー氏は「これまで通信インフラはARMのターゲットに含まれていなかったが、ARMv8で初めて通信インフラの市場をターゲットの1つとした。ARMv8を採用することで、ツールやソフトウェアなどARMがすでに構築したエコシステムが利用でき、顧客の選択の幅が広がるうえ、さまざまな機能が利用できるようになるまでの時間が短縮されることになる」とした。

ブロードコムでネットワークプロセッサの開発を担当しているのは、同社に買収された旧NetLogicだった部門だ。NetLogicではMIPS 64bitプロセッサを採用していたが、ARMv8の発表により、通信市場をターゲットにしたARMの動きに乗って、今回の製品の開発を行った。

最近のプロセッサでは命令を「マイクロ命令」と呼ばれる小さな命令に分解し、これを実行する構成を取るものが多い。アーキテクチャ上の命令をマイクロ命令に変換する部分を「デコーダー」というが、かつてデコーダーは、命令を後段のパイプラインで実行しやすいビットパターンに変換するものだった。しかし、現在では、これをマイクロ命令に変換する。違いは、1つのアーキテクチャ命令が複数のマイクロ命令に変換される場合もあるという点だ。

2011年に発表されたARMv8は64bitアーキテクチャとしては後発で、他社の64bitアーキテクチャの評価が行われたあとに作られたもので、命令体系としてはかなり整然とした、ある意味「最後の64bitアーキテクチャ」なのである。こうしたアーキテクチャ上の命令セットが比較的整然としている場合には、命令セットの変更は比較的容易だが、そうでない場合は容易に変更できるとはいかないこともある。

おそらくは、MIPS 64bitなどで使った実行エンジンなどをベースにARMv8に対応するために、「独自」アーキテクチャにならざるを得ないのだと推測できる。また、現在ARMが発表している64bitプロセッサ実装であるCortex-A53/57がネットワーク処理に最適というわけでもない。

さて、今回のプロセッサアーキテクチャを具体的に採用した製品に関して、ブロードコムはNFVとの関係を強調している。NFV(Network Function Virturaization)とは、EU圏のETSI(European Telecommunications Standards Institute)やLinaro Networking Groupなどで定義する「ネットワーク機能仮想化」の仕組みのことだ。

簡単にいうと、仮想化したネットワーク機器を前提に上位のシステムを構築することで、特定の機器や専用ハードウェアに依存することなくネットワークを構築するための仕組み。これは、現在のトレンドの1つで、方向性としては、汎用性の高いコンピュータシステムに通信用のカードなどを組み合わせて、通信インフラ(コアネットワークなど)を構築することを目指す方向性だ。

ある種の「流行」ではあるが、ARMなどは、既存のエコシステムをベースにNFVなどを足がかりにして通信インフラ分野にも進出したいと考えている。こうした思惑と、すでに通信インフラ分野向けのデバイスビジネスを展開しているブロードコムの思惑が一致し、今回の通信インフラ向けプロセッサの発表となったのだと思われる。

なお、ブロードコムとしては、NFVを強調するのは、同社の顧客である通信機器メーカーの顧客(おそらくは通信事業者)がNFVを要求しているためで、NFVに分野を限ったものではないが、同社としてもアーキテクチャが一新となる新規プロセッサ立ち上げの足がかりとして見ているとのことだ。もちろん、ほかの分野やさまざまな企業がターゲットだが、取りあえず、ネットワーク分野から攻め入るとのことようだ。