富士通研究所およびFujitsu Laboratories of Americaは18日、CPU間などのデータ通信において世界最高速、32Gbps伝送が可能な送受信回路を開発したと発表した。同社ではCPUを多数接続した次世代サーバやスパコンの性能向上を見込んでいる。

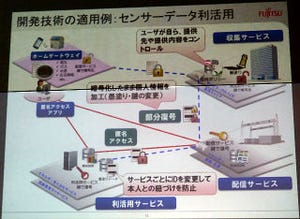

CPU間などのデータ通信部は、送信部と受信部から成り、そのうち受信部は伝送路で劣化した信号品質を補償する「損失補償回路」と、その補償した信号から元のデータを読み取る「受信回路」から構成される。

今回同社が開発したのは、新方式の送信回路、受信回路、および信号品質の劣化を補償する損失補償回路。

送信回路では通常、多チャンネルのデータを、数段階を経て1チャンネルに多重化して送信する。新技術では、その最終段の多重化回路(2:1変換回路)を不要とする送信回路を開発。これにより高速化を図ったほか、上記の回路を省くことで該当部の消費電力も約30%低減したという。

「損失補償回路」は、プリント基板配線の伝送路などを通じて送られたデータ信号の損失を補償する回路。データ信号は伝送路の距離が長く、高速化するほど損失が大きくなる。

従来の伝送速度では、データ信号波形の高域側で発生する損失のみ補償していたが、データの高速伝送にともない、低域側のデータ信号の損失も問題となり、新たに低域側の信号損失を補償する回路を開発。従来32Gbpsでは実現できなかった80cmの伝送距離でも、データの読み取りが可能となった。

また、「損失補償回路」によって整形された信号から元データを読み取る「受信回路」は、速度(周波数)とタイミング(位相)を同期させて、信号をサンプリングする。従来、データを取り込むタイミング誤差をタイミング誤差検出部で元データから検出し、タイミング調整回路で同期させていた。

新技術では、同期していないクロックで一旦信号をサンプリングし、実際にサンプリングされた二つの信号を元に電圧補間処理することで、クロックと同期したタイミングでの仮想信号を合成するデータ補間方式(データインターポレーション方式)を開発。精度な時間軸方向の分解能が要求されるタイミング調整回路が不要となり、今後のさらなる高速化にも対応可能という。

同社ではこの技術により、「次世代サーバやスーパーコンピュータなどの性能向上に寄与することが期待される」とし、今後は同技術をビックデータを扱う分野へ適用させていく。