Cortex-A57の詳細

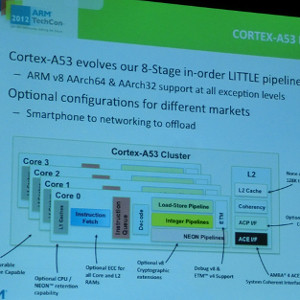

セッションで公開されたスライド(Photo06)は、図が縮小されていて鮮明ではない。このため、とりあえず、おおまかな構成がわかるように注釈を図に付けた(図01#%Block%#)。

A57のプロセッサは、コア部分と、コア間で共有するL2モジュール、割り込み/デバッグ/トレースモジュールからなる。L2モジュールには、他のクラスタのキャッシュ状態を監視、取得するスヌープ機構が組み込まれている。L2キャッシュは、クラスタ内で最大4つのコア間で共有するが、それぞれのコア用のインターフェース、命令プリフェッチャーを備える。構成は16Wayのセットアソシアティブである。また、L2のTLBは1024エントリで4ウェイのセットアソシアティブで、ページウォーク(TLBがヒットしなかったときにメモリ上のページテーブルを検索すること)用のキャッシュを各レベルのテーブル用に持つ。

この後段になる命令フェッチ側に48キロバイト3WayのL1キャッシュと、48エントリのL1 TLBがおかれている。また、ここには分岐予測機構とブランチターゲットバッファがある。分岐予測には、パス履歴を持つ間接ブランチ(レジスタの内容を飛び先とするブランチ)用の予測機構が含まれている。

フェッチされた命令は、デコーダーに送られるが、ここでは3命令の同時デコードが可能。デコードされた命令はディスパッチャーでパイプラインへ送られるが、このディスパッチャは3命令の同時発行が可能だという。

レジスタファイルだが、A57は、アウトオブオーダー実行であり、レジスタリネーミング機構を持つ。AArch 32では、16個のレジスタとさらにバンク切り替え分をいれて31個の32bitレジスタを扱う。AArch64には、やはり31個の汎用レジスタがある(ただし64bit)。A53では、AArch32とAArch64のレジスタパスを共用していたが、同様の機構はA57にもあるようだ。ただし、物理レジスタ数は、A53よりも多いと推定される。

命令実行パイプラインは、ブランチ、かけ算/割り算/積和、その他の整数演算(x2)、ロードストア(各1つづつ)、SIMD演算(かけ算/割り算とその他の演算の2つのパス)の合計8つのパスがある。ここに対して、ディスパッチャーは同時に3命令の発行が可能になっている。

整数部分は、ブランチ、かけ算/割り算/積和、その他の整数演算2つで合計4つ命令を同時処理できる。64bitに対応しているが、32bit演算時には、不要な部分を非アクティブ化することで消費電力を減らす機能を持つ。

NEON部はオプションで暗号アクセラレータ処理(および拡張命令)を設計時に追加することが可能。AES、SHA-1、SHA2-256などの計算が最大5倍に高速化されるという。

NEONは、128bitのSIMD演算機能で4つの単精度浮動小数点数値(32bit)または2つの倍精度浮動小数点数値(64bit)の同時処理が可能なもの。内部には11の演算ユニットがあり、浮動小数点の割り算ユニットは2つ、単精度と倍精度のハイブリッド形式で消費電力に対しての最適化が行われているという。

ロードストアユニットには、32キロバイトのL1データキャッシュが含まれている。これは、2Way DCで、L2との重複を許す構造だ。また、データ用のTLBは32エントリでフルアソシアティブ。A57は、ソフトウェアからは64bitのアドレスを扱うが、物理アドレスラインは44ビット、またハードウェア上は48ビットのアドレスが有効である。またアドレス空間ID(ASID)は16bitあり、64k個のプロセスを識別することが可能だ。