インスタントオン

複雑なシステムでは、デバイスごとの仕様に正確に従い、正しい順序で各デバイスに電源を供給することが非常に重要です。この機能がマイクロプロセッサに依存していた場合は、プロセッサの起動シーケンスが終了し、システムの残りの部分に電源が供給されるまで、システムが待たされることになります。そのような場合は、起動に時間がかかったり、他のデバイスに無秩序に信号が供給されるなど、多くの問題が発生します。

プラットホーム・マネージャは、コンフィグレーション用に内蔵不揮発性メモリを使用することで、この問題を防止します。

バックプレーン管理と活線挿抜

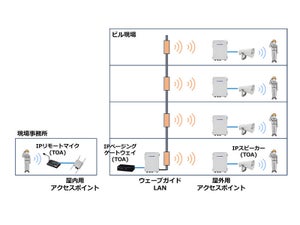

一般的にボードがラックマウントまたはシェルフマウントされる通信システムでは、プラグイン・ボードがシェルフマネージャと通信して、ボードのコンフィグレーションに関する情報が提供されます。シェルフマネージャは、正しいカードが挿入されているかどうか確認します。シェルフマネージャから電源投入コマンドを受信しない限り、ペイロードはオンになりません。

リセットツリー

プラットホーム・マネージャには、リセット分配用の効率的メカニズムが用意されています。多くの場合、ボード上の各デバイスは制御された方法でリセットする必要があります。PLLロック完了、メモリ・コントローラ・レディ、FPGA処理終了など種々のリセットと、システムクロックとの同期が必要になることもあります。設計によっては、リセットのシーケンス制御を行うことで、ピーク消費電流を抑え、起動の信頼性を高める必要があります。

代表的アプリケーション

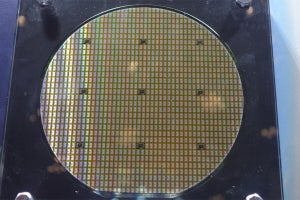

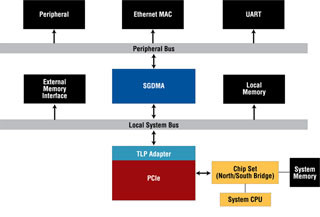

プラットホーム・マネージャの代表的アプリケーションを図3に示します。この例で、プラットホーム・マネージャは12系統の電源の故障を検出できます。各系統は黒い点で表してあります。最大8系統のトリミングが可能ですが、重要機能であるため詳しく後述します。このデバイスは情報を取得し、それを不揮発性SPIメモリに記録することもできます。電圧モニタ機能は、各種電源出力の差動出力に接続された状態を示してあります。

VID制御

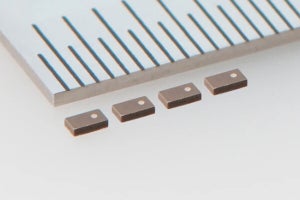

45nm以下で製造された一部のASICおよびCPUデバイスは、そのデータシート性能を満たすため、種々のコア電圧が必要になることがあります。必要なコア電圧はエンコードされ、電圧ID(VID)としてボード管理ロジックから読み取り可能です。こうしたときには厳しい要求に応えるため、正確で高価な電源の使用が必要になることがよくあります。VID情報を使用することで、パワーマネージャはマージンおよびトリム回路を使用して、種々の電源電圧を正確に制御できるため、結果的に低コストなDC-DCコンバータの利用が可能になります。

設計と評価

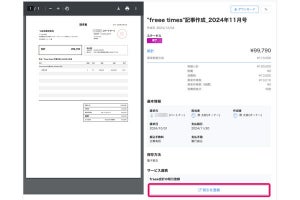

設計サイクルを容易にし、短縮するため、Latticeでは多数のツールとオプションを用意しています。このファミリには、PAC-Designer 6.0ソフトウェア、およびispLever設計ソフトウェアツールのStarterバージョンSP1が対応しています。

これらはLatticeのWebサイトからダウンロード可能な無償ツールです。また、無償の参照デザイン4つと無償のIPコアが3つあり、不揮発性メモリへの故障ログ、閉ループ・マージン管理、I2CまたはSPIバス・マスタへのインタフェースなどの共通機能が実装されます。さらに、デモデザインとマニュアル一式がそろった評価ボードが含まれた、低コストなプラットホーム・マネージャ開発キットを購入可能です。このボードを使用することでユーザは5分以内にハードウェア動作を確認し、また用意されたソースコードを再コンパイルして、30分以内に動作確認の出発点とすることができます。エンジニアにとっては、独自設計に本格的にとりかかる前に、このデバイスの機能に習熟することのできる非常に貴重な手段になります。

まとめ

プラットホーム・マネージャは柔軟なプログラマブル・デバイスであり、カスタマイズすることで、エンジニアが最新の複雑なシステムに電源および制御機能を提供するうえで直面する多くの問題を解決できます。こうした機能の多くが1つのデバイスに集積されたプラットホーム・マネージャは、部品点数を減らすことでシステム全体のコストを削減し、システムの信頼性を大幅に高めることができます。

著者紹介

著者:Shyam Chandra

役職:Lattice Semiconductor プロダクトマーケティングマネジャー

Latticeでは、特にパワーマネジメント関連を担当。同社入社前は、営業やアプリケーションエンジニアとしてVantisやAMDなどに勤務していた。

インド工科大学で電子工学の修士を取得している。